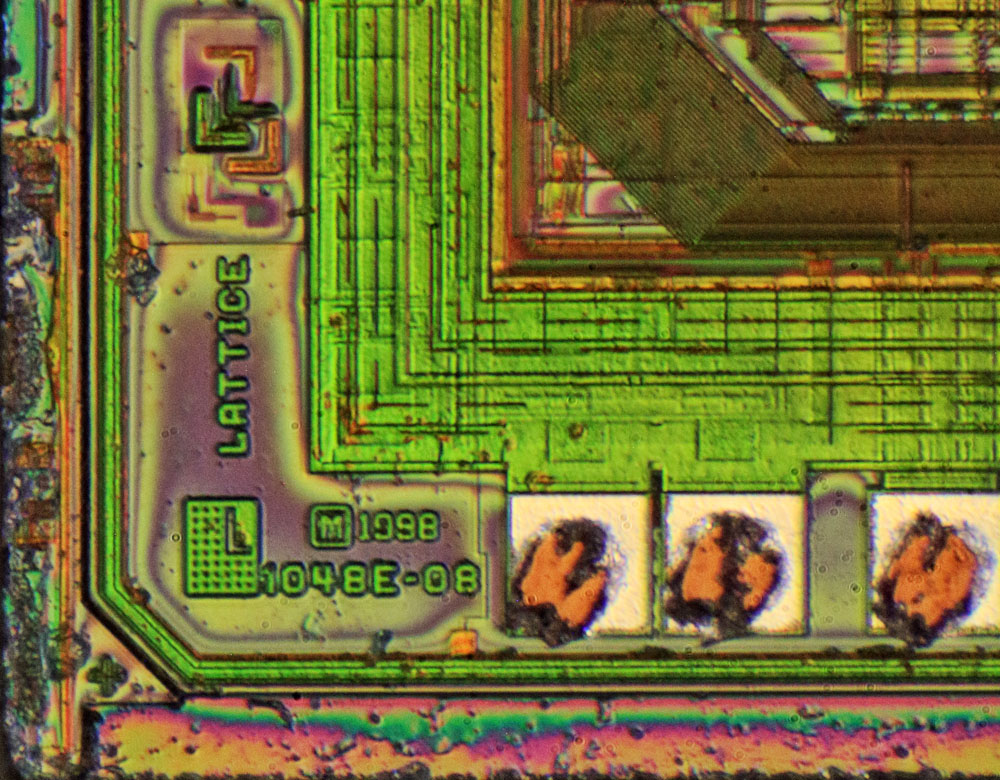

Der LSI1048 ist der größte CPLD aus der Produktfamilie, zu der auch der LSI1016 und der LSI1024 gehören. Der hier vorliegende ispLSI1048E stellt bereits eine neuere Generation dar. Im zugehörigen Datenblatt findet sich der Hinweis, dass der Baustein funktions- und pinkompatibel zum ispLSI1048C ist. Im Datenblatt des ispLSI1048C findet sich wiederum der Hinweis, dass im Vergleich zum ursprünglichen ispLSI1048 zwei Eingänge und zwei Pins zur Deaktivierung der Ausgänge hinzugekommen sind.

Als isp-Variante kann man den ispLSI1048E auch innerhalb einer Schaltung programmieren. Er bietet 48 Logik Blöcke, 8000 Gates, 288 Register und 96 I/Os. Die Gehäuseform PQFP-128 bietet die notwendigen Schnittstellen nach außen. Die Zahl 70 gibt die maximal zulässige Taktfrequenz mit 70MHz an. Laut Datenblatt ermöglichen die schnellsten Varianten Taktfrequenzen von bis zu 125MHz.

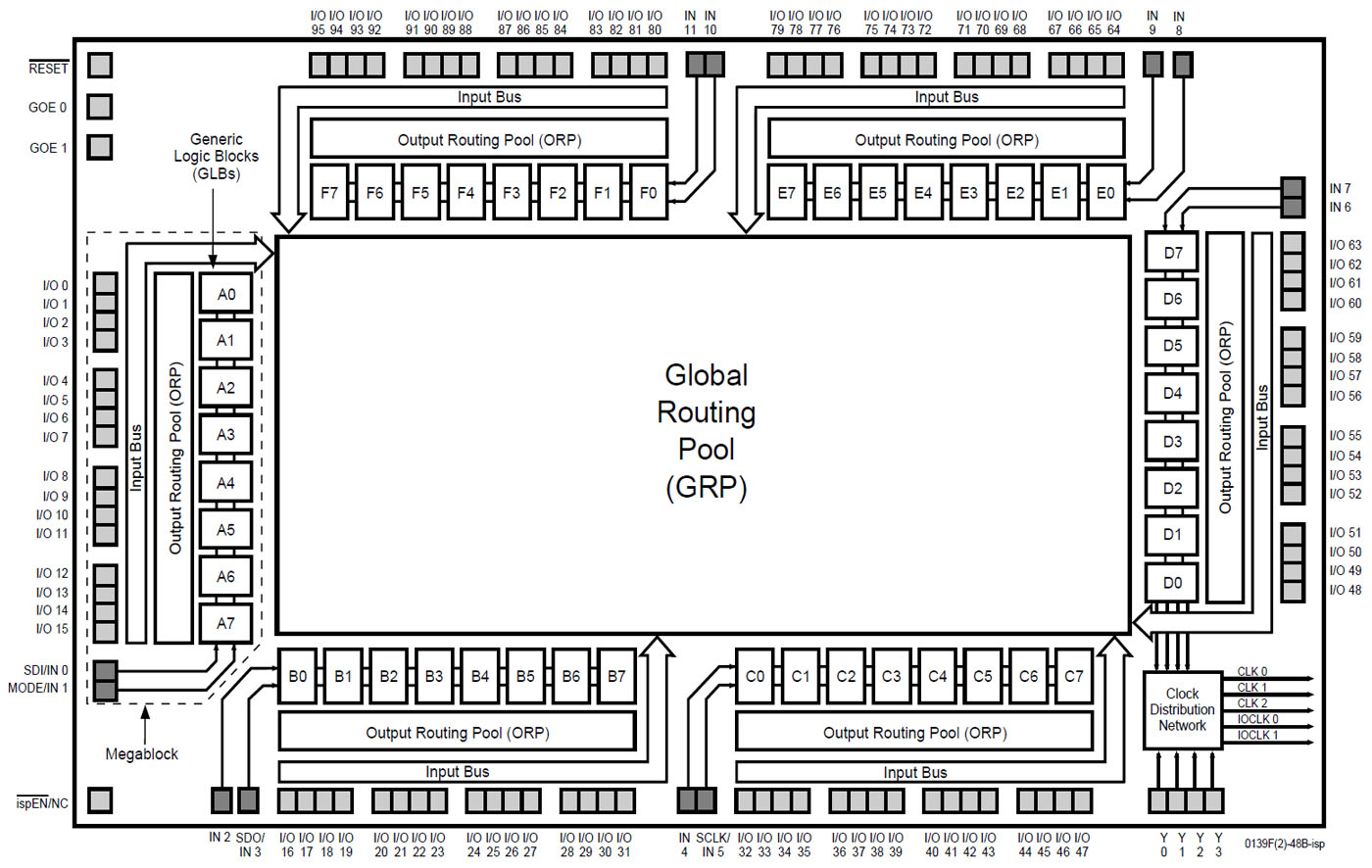

Der Aufbau ist dem LSI1016 und dem LSI1024 sehr ähnlich, hier wurden lediglich sechs der sogenannten Megablöcke integriert.

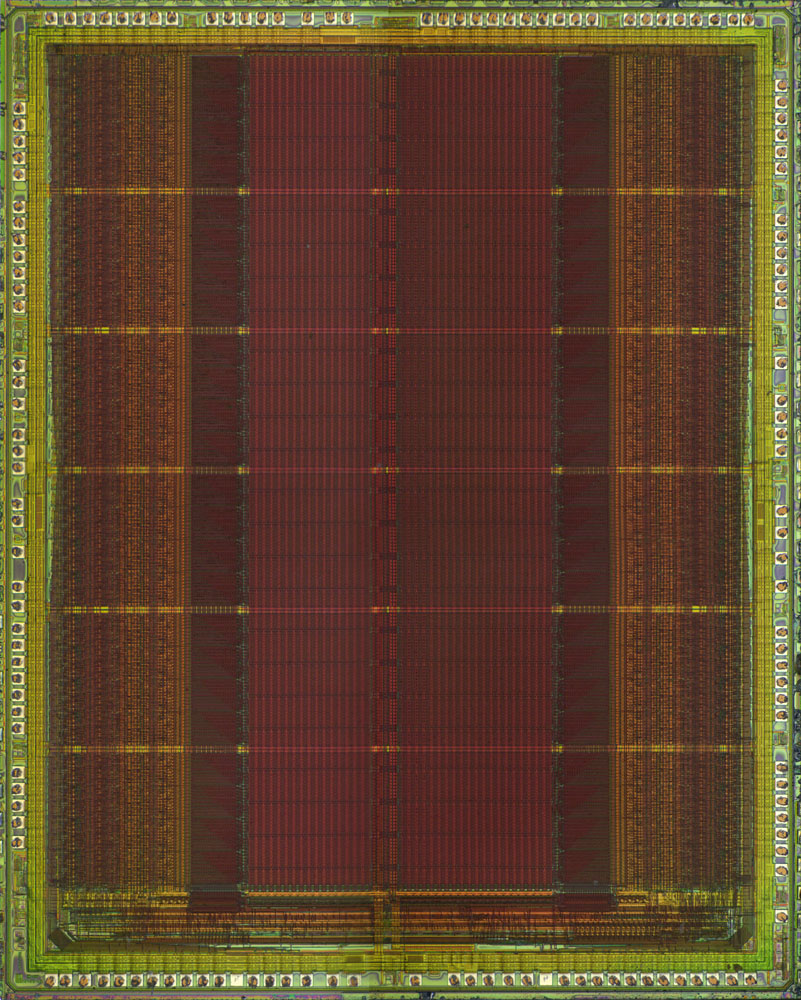

Bei den Abmessungen des Dies kann man deutlich die Weiterentwicklung zur Generation E erkennen. Mit 5,9mm x 4,7mm ist das Die trotz der stark erweiterten Funktionalität merklich kleiner als das Die des LSI1024.

Das Design wurde sieben Jahre nach dem LSI1024 entwickelt. Die minimalen Strukturbreiten sind merklich kleiner.

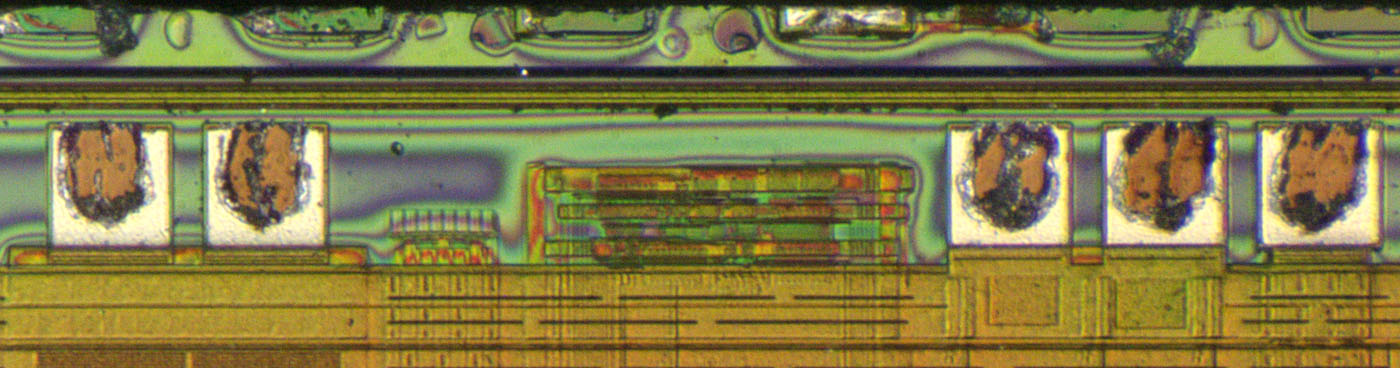

Wie bei den anderen CPLDs wurden auch hier zwischen den Bondpads verschiedene Schaltungsteile integriert.

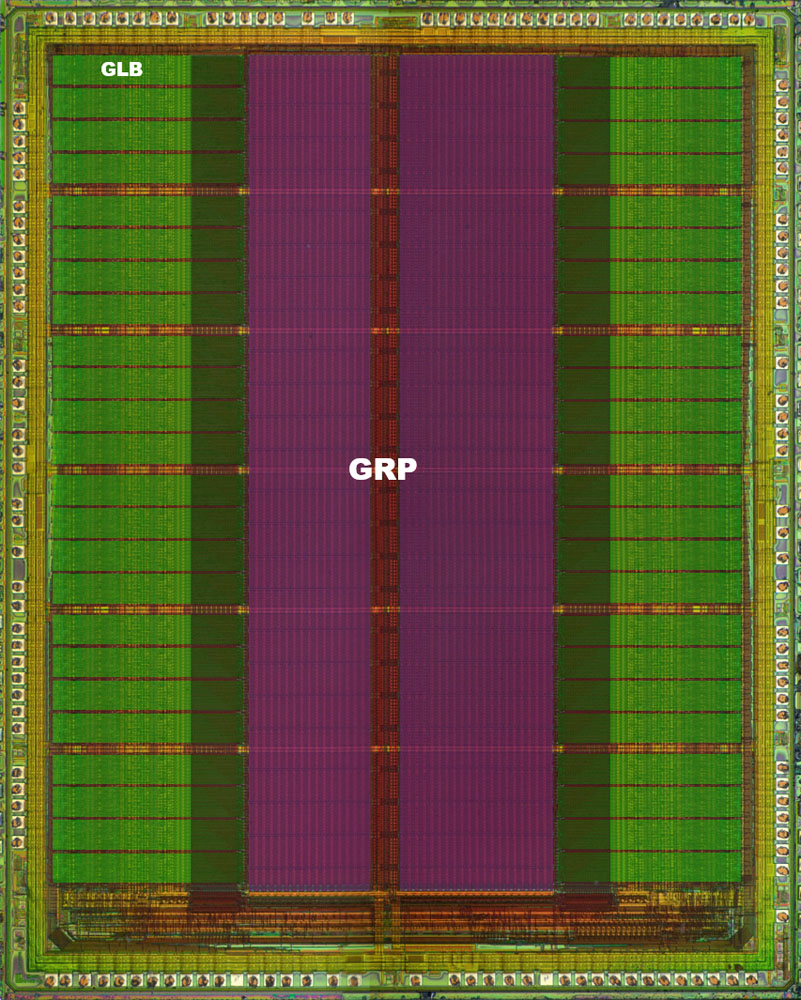

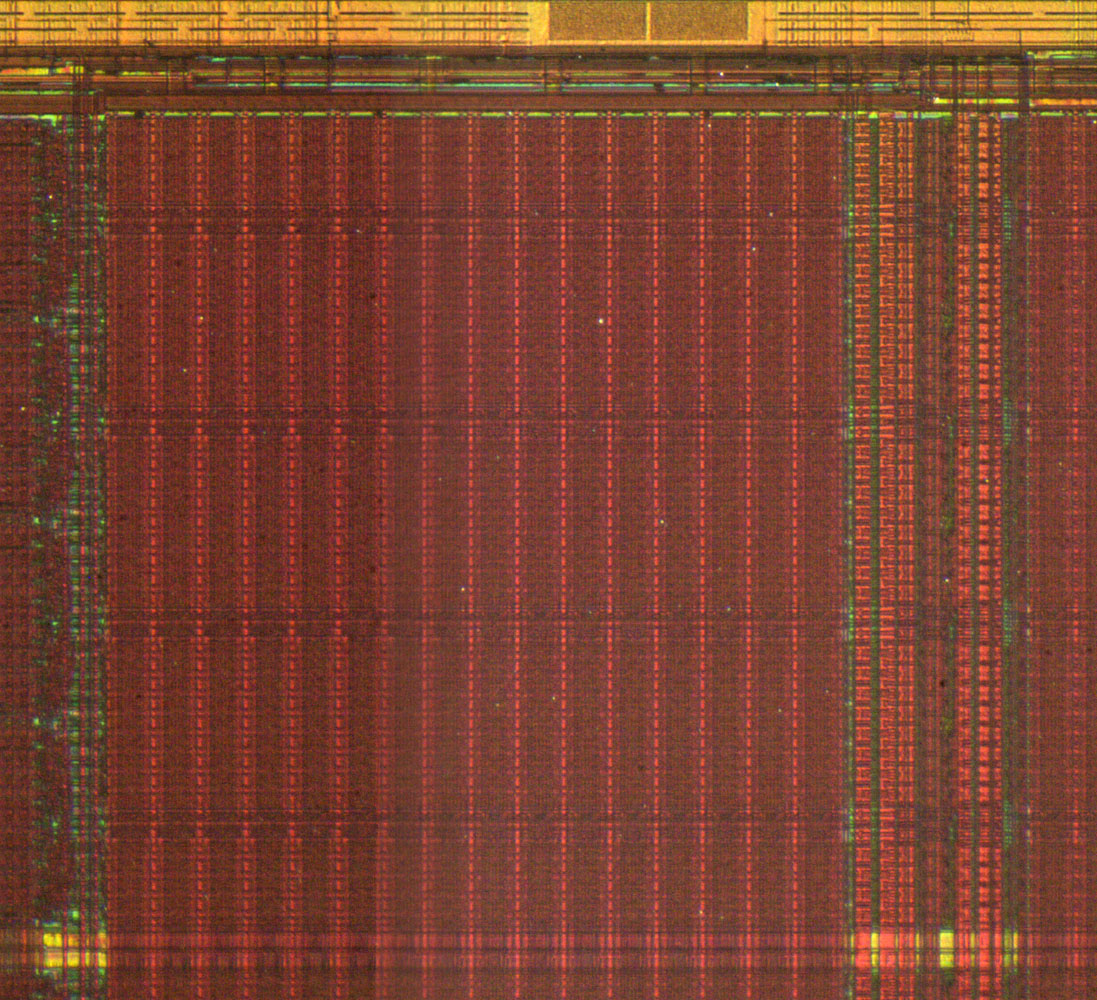

Trotz der höheren Integrationsdichte lassen sich die großen Schaltungsblöcke gut identifizieren. Die Global Logic Blöcke (GLB, grün) sind in Vierer-Gruppen integriert. Auch die Logik Arrays der Global Logic Blöcke sind zu erkennen (dunkelgrün). Zwischen den rechts und links platzierten Global Logic Blöcken befindet sich der Global Routing Pool (GRP, violett).

Dieser Ausschnitt zeigt eine der GLB-Vierer-Gruppen.

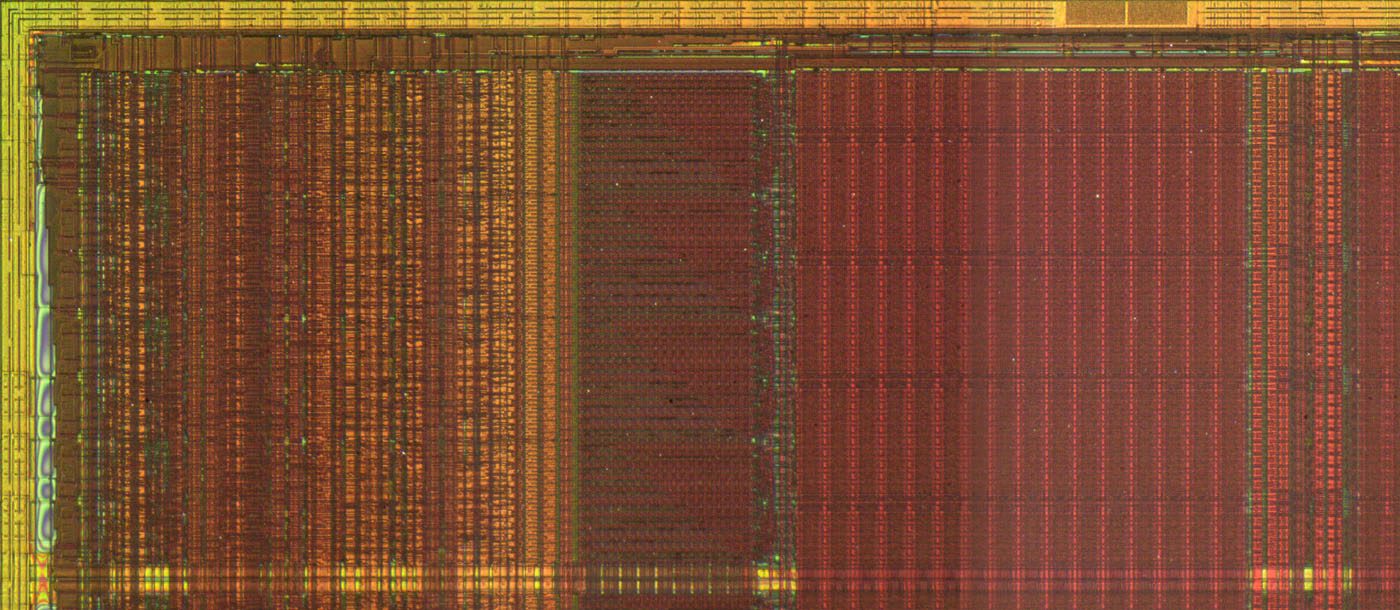

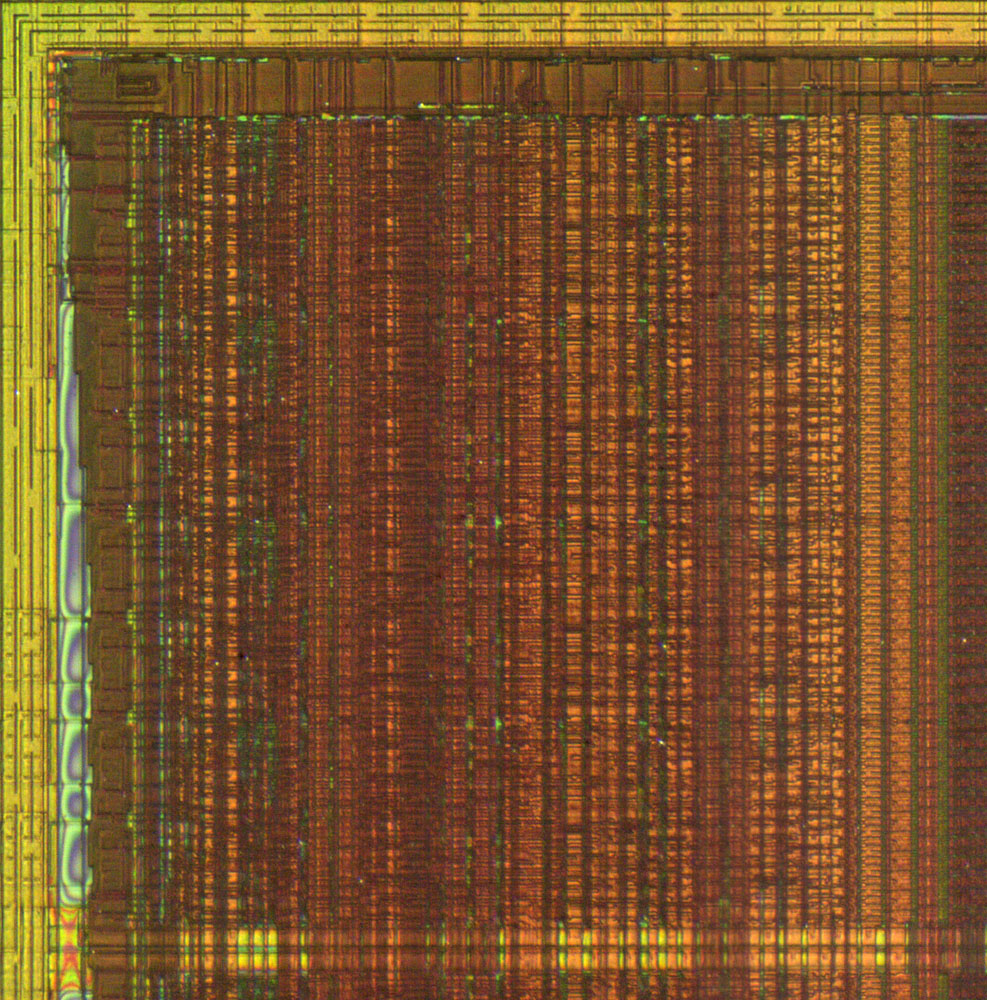

Die Global Logic Blöcke sind wie beim LSI1016 und beim LSI1024 etwas unregelmäßig. Die I/O-Zellen lassen sich beim LSI1048E nicht unterscheiden. Am linken Rand ist lediglich der breite Bus zu erkennen, der höchstwahrscheinlich die Ausgangssignale der Global Logic Blöcke weiterleitet.

Die Logik Arrays der Global Logic Blöcke besitzen den bekannten treppenförmigen Aufbau, der sich hier aber nur schwach abzeichnet.

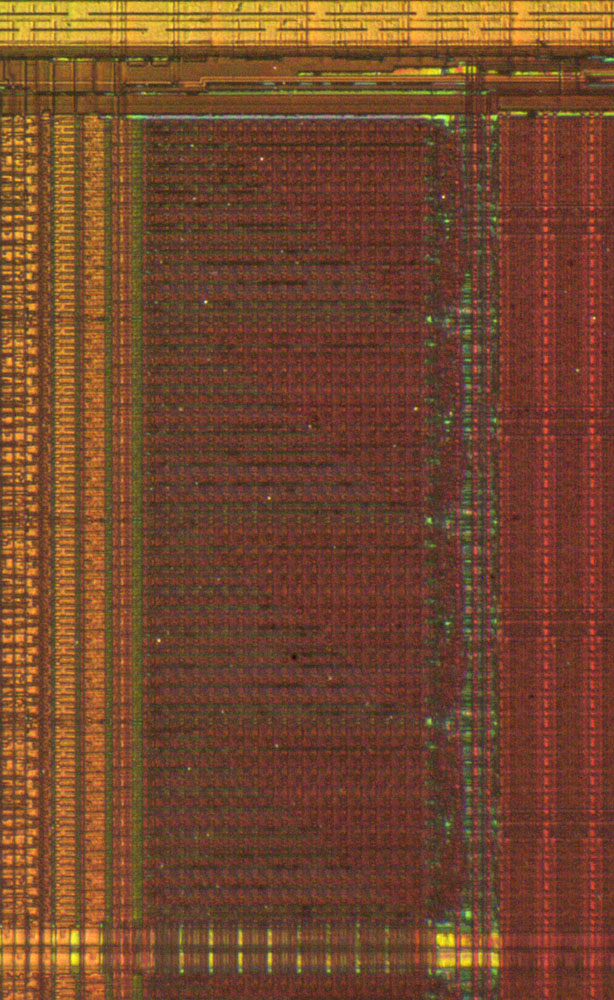

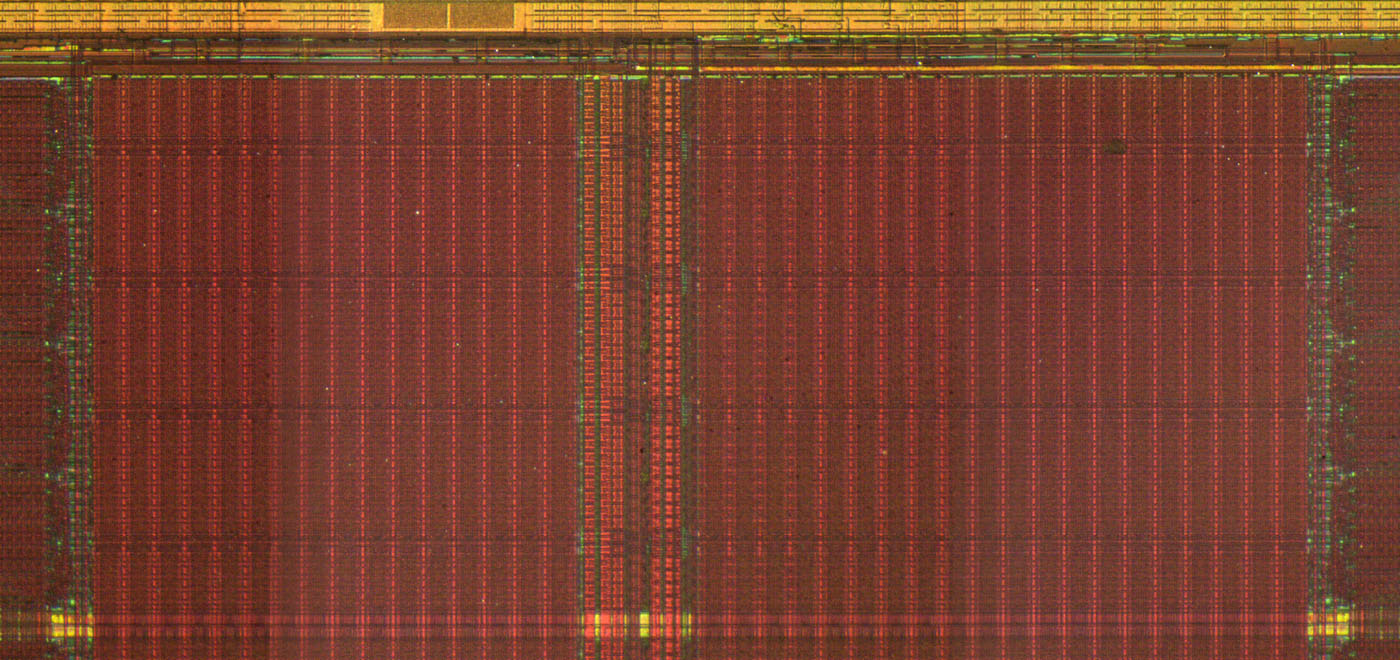

Der Global Routing Pool ist sehr gleichmäßig aufgebaut.

Warum der Global Routing Pool unsymmetrisch aufgebaut ist, erschließt sich nicht.