Der LSI106 ist das kleinste Modell einer von Lattice entwickelten CPLD-Reihe. Die isp-Varianten können innerhalb einer Schaltung programmiert werden.

Die Variante 1016 enthält laut Datenblatt 16 Logik Blöcke, 2000 Gates, 96 Register und 36 I/Os. Die maximale Taktfrequenz liegt bei 80MHz, die Signalverzögerung bei 15ns.

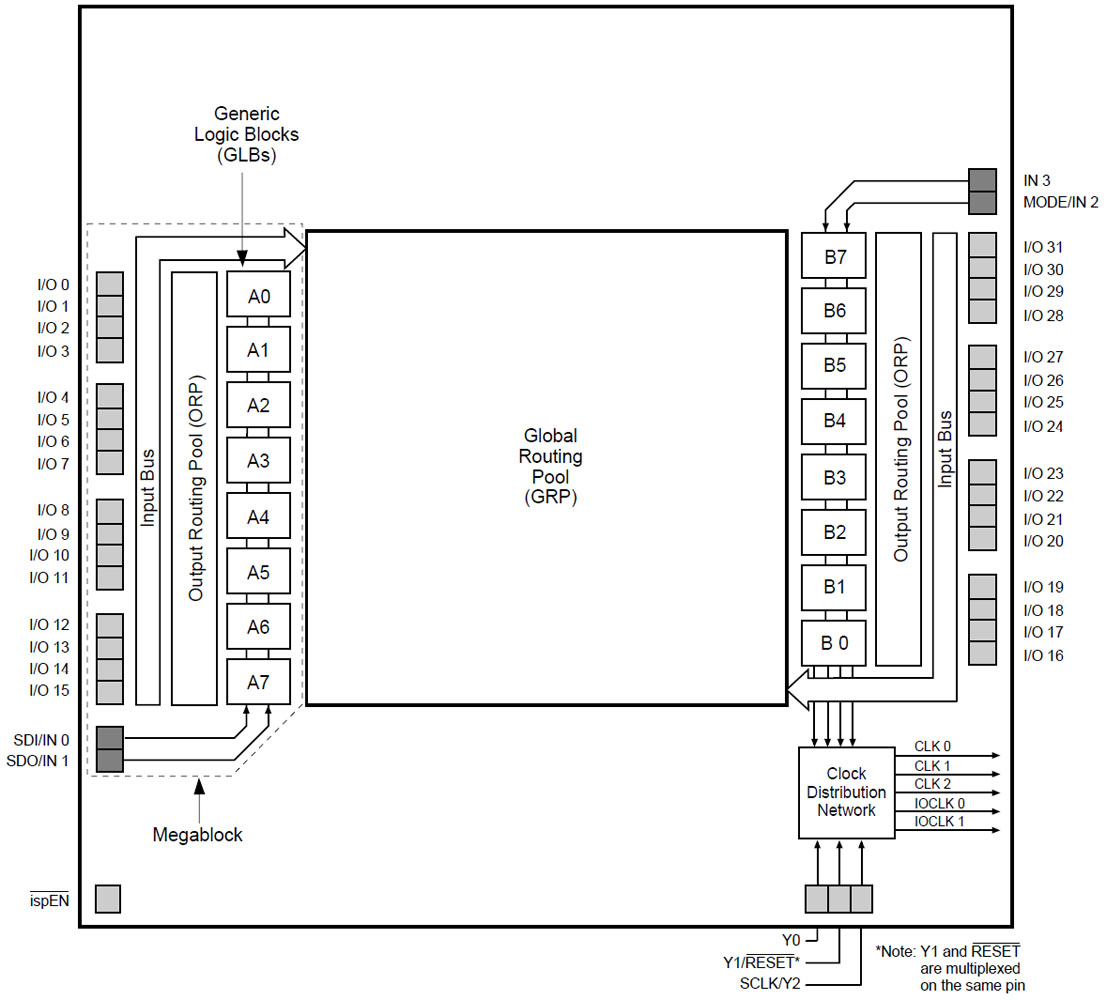

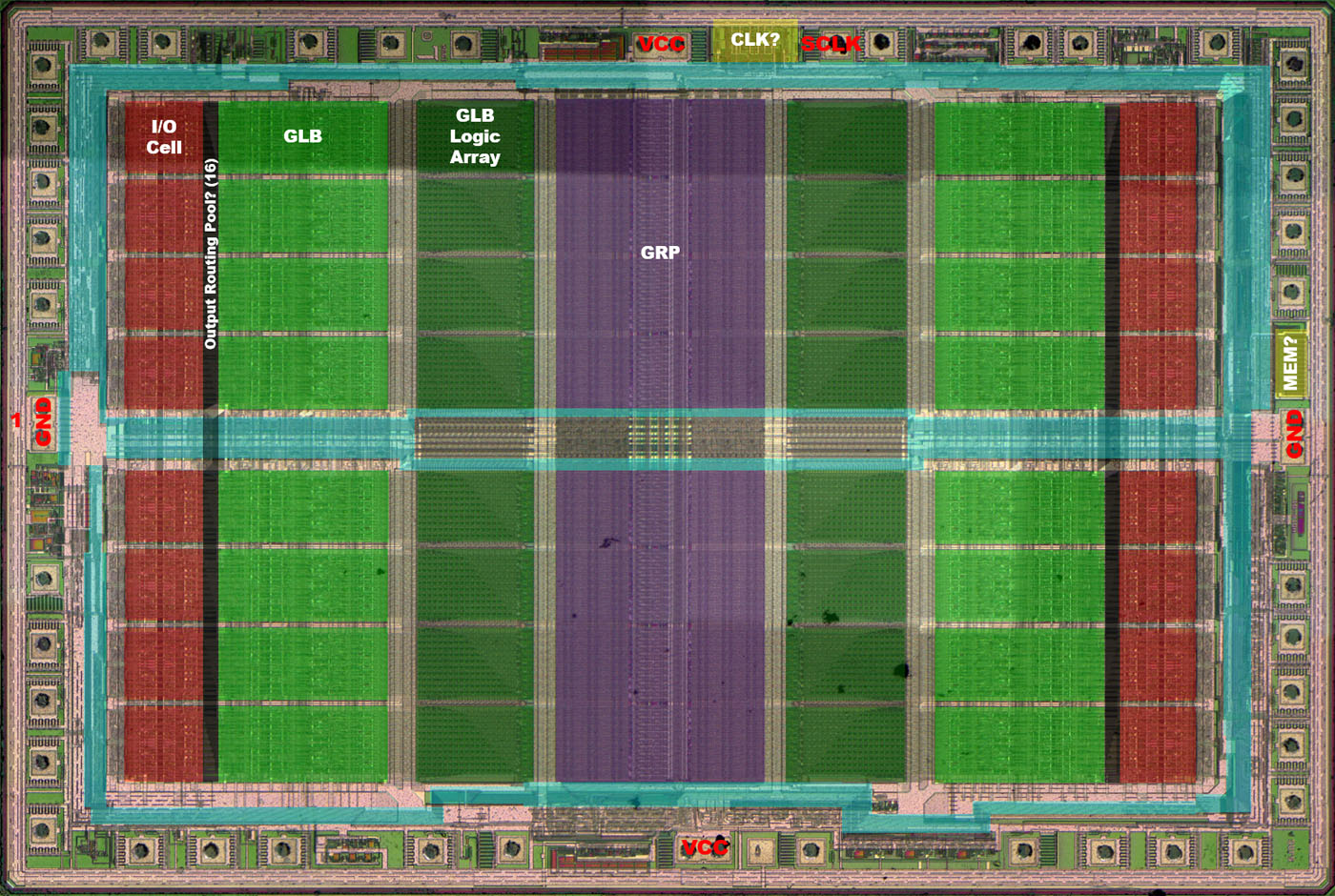

Das "pLSI and ispLSI Data Book and Handbook" von Lattice enthält einige Blockschaltbilder, die den Aufbau des CPLDs darstellen und erklären. Der ispLSI1016 bietet zwei sogenannte Mega-Blöcke, die um einen Global-Routing-Pool (GRP) angeordnet sind. Über den Global-Routing-Pool wird ein Großteil der gewünschten Verbindungen realisiert. Laut ispLSI-Handbuch befindet sich an jedem konfigurierbaren Verbindungsknoten eine sogenannte E²CMOS-Speicherzelle, in der der gewünschte Status der Verbindung vor Ort abgelegt ist.

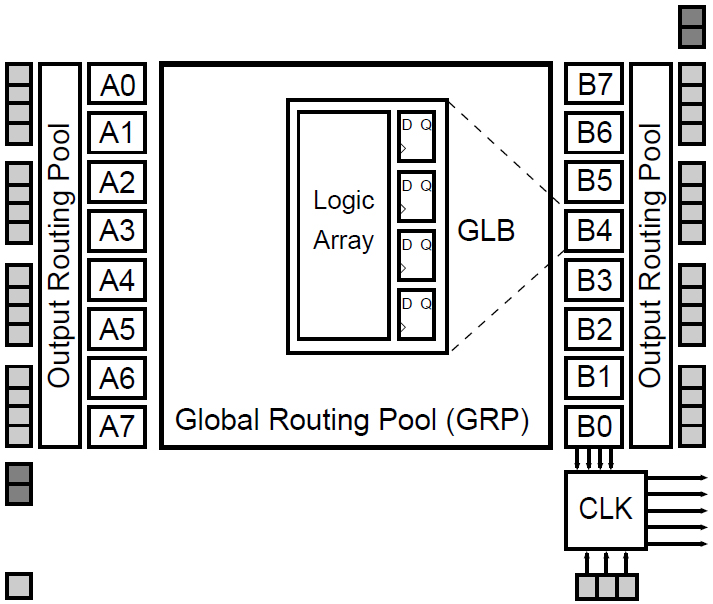

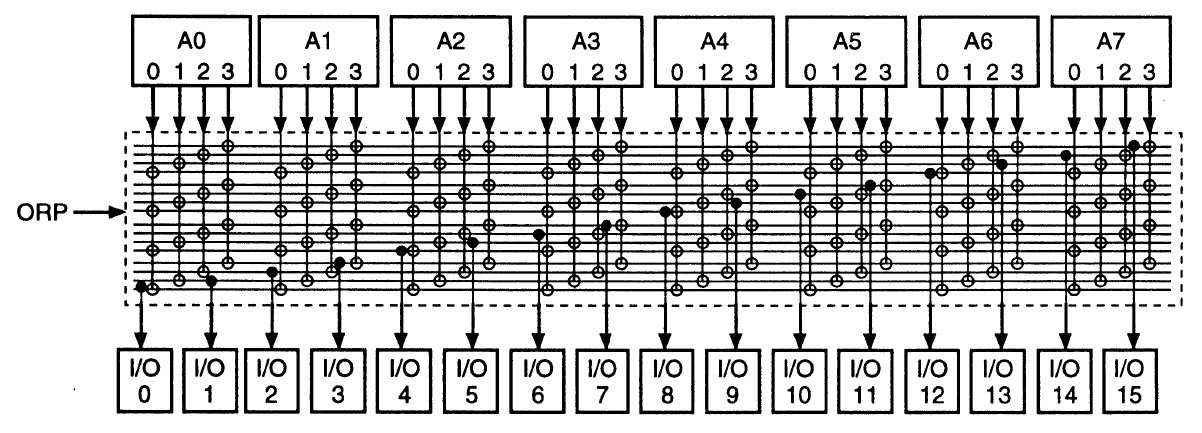

Jeder der zwei Megablöcke beinhaltet acht Global-Logic-Blöcke (GLB), die zum einen an den Global-Routing-Pool angebunden sind und zum anderen einen Output Routing Pool (ORP) besitzen. Über den Output-Routing-Pool werden die Pins des ispLSI1016 an die Global-Logic-Blöcke angebunden. Die I/Os, die als Eingänge genutzt werden, sind direkt mit dem Global-Routing-Pool verbunden. Ausnahmen sind die Eingänge IN0/IN1 und IN2/IN3, die fest dem linken beziehungsweise dem rechten Megablock zugeordnet sind.

Die Systemtakte des ispLSI1016 lassen sich umfangreich konfigurieren. Der Pin Y0 ist fest mit dem grundlegenden Systemtakt CLK0 verbunden. Über die Pins Y1, Y2 und ein Logikarray kann man vier weitere Systemtakte erzeugen.

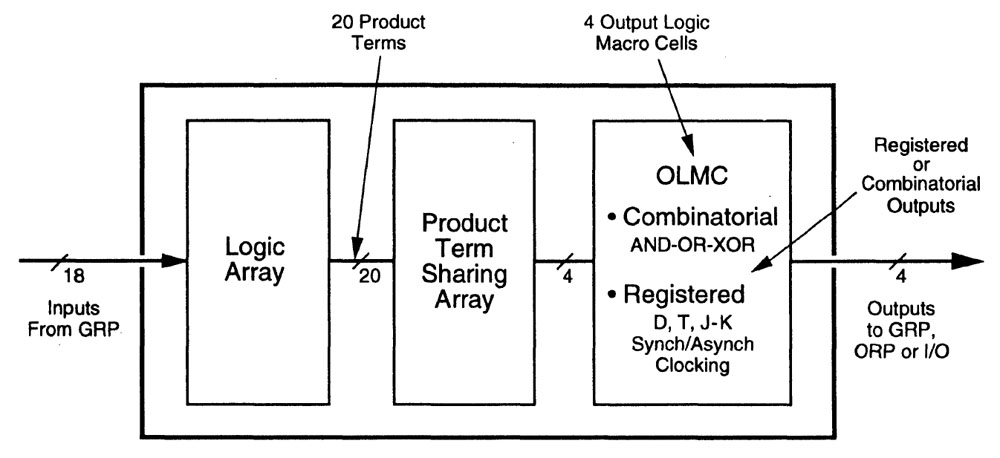

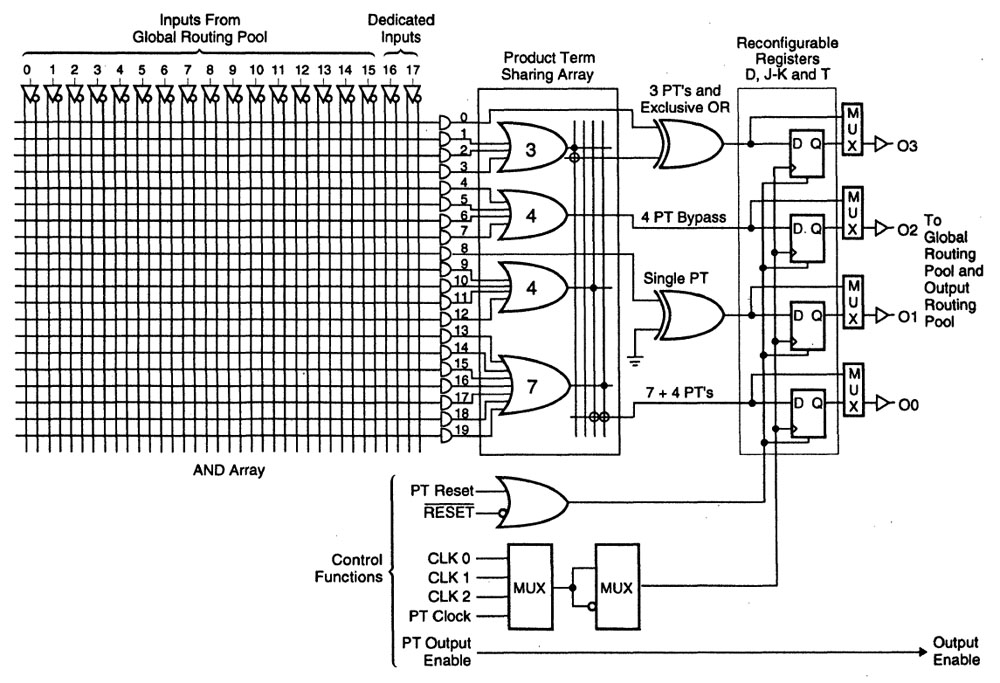

Jeder Global-Logic-Block ist über 16 Leitungen mit dem Global-Routing-Pool verbunden. Außerdem führen die zwei fest zugeordneten Eingänge durch alle Global-Logic-Blöcke eines Mega-Blocks. Die 18 Eingangssignale werden gepuffert und differentiell in eine lokale Verbindungsmatrix mit E²CMOS-Zellen geführt.

Auf die Verbindungsmatrix des Global-Logic-Blocks folgt ein sogenanntes Product-Term-Sharing-Array mit verschiedenen ODER-Gattern (Product Terms). Die ODER-Gatter können unterschiedlich, aber nicht beliebige ausgewählt und kombiniert werden. Die hier dargestellte Variante ist nur eine Möglichkeit unter Vielen.

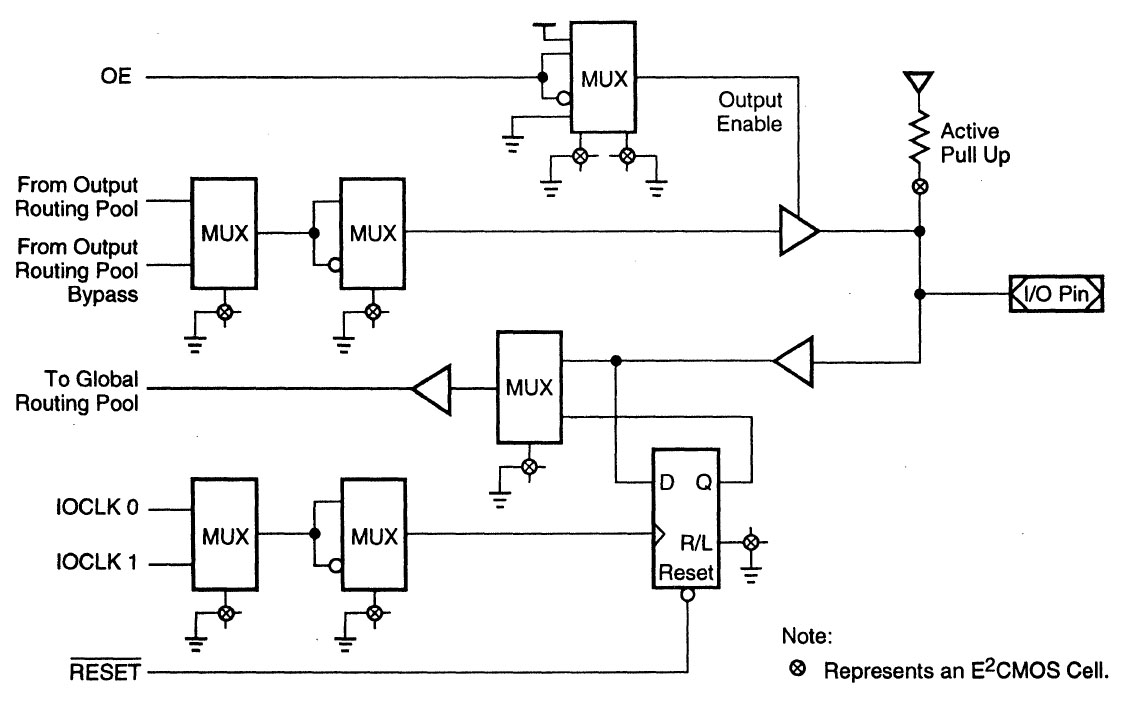

Am Ausgang eines jeden Global-Logic-Blocks befinden sich vier Output-Logik-Macro-Zellen (OLMC). Sie ermöglichen es den Ausgangspegel direkt über Gatter auszugeben oder mit Hilfe von Flip-Flops zwischenzuspeichern. Die Flip-Flops lassen sich synchron und asynchron zum Systemtakt betreiben. Die vier Ausgänge der Logik-Blöcke können entweder zurück zum Global-Routing-Pool geführt oder über den Output-Routing-Pool zu einem Pin des ispLSI1016 übertragen werden.

Der Output-Routing-Pool (ORP) ermöglicht diverse, aber nicht beliebige Verbindungen zwischen den Ausgängen der Global-Logic-Blöcke und den I/O-Zellen des ispLSI1016.

Die I/O-Zellen beinhalten die notwendige Logik zur Konfiguration der Arbeitsweise und zur Signalaufbereitung.

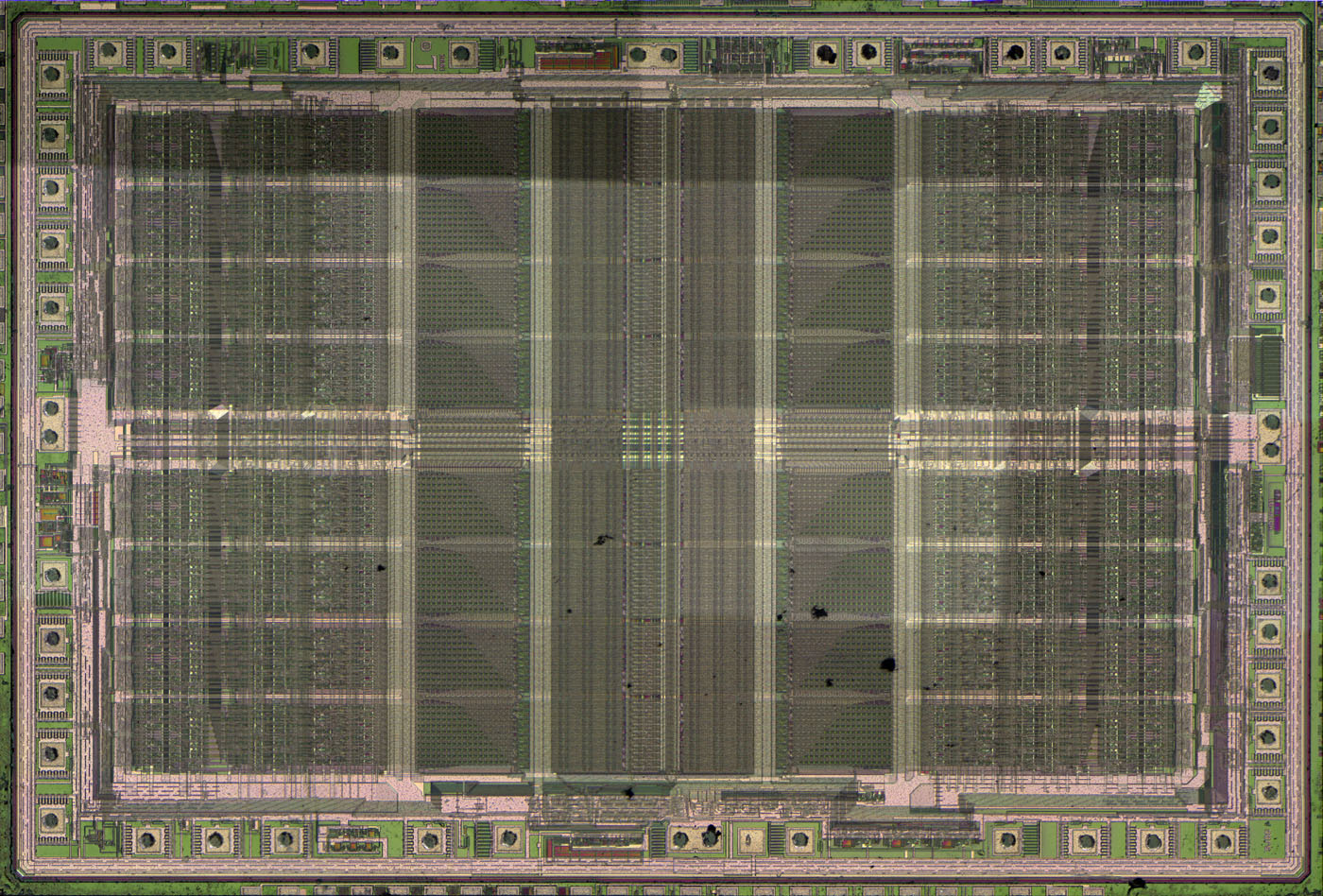

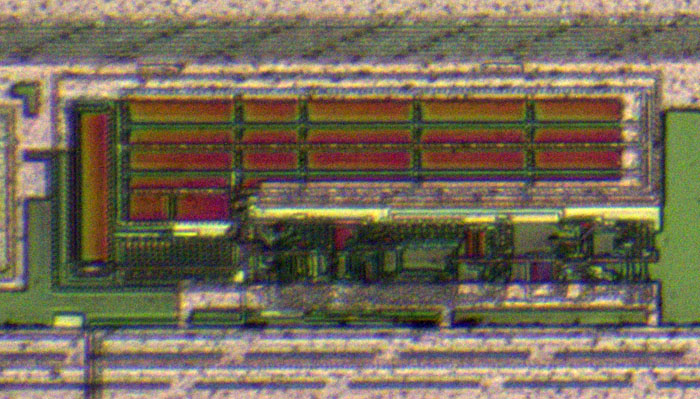

Wie zu erwarten war, ist das Die des ispLSI1016 sehr groß: 6,1mm x 4,1mm. Das Datenblatt gibt an, dass die Herstellung mit einem 0,8µm-Prozess erfolgt.

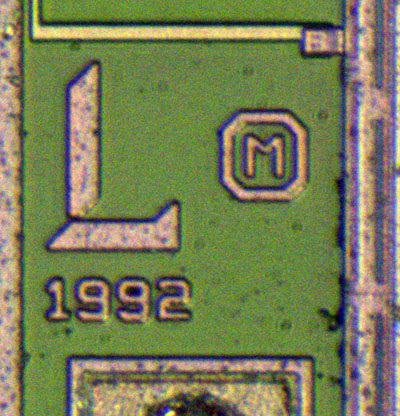

Das Design stammt aus dem Jahr 1992.

Die Zeichenfolge HD16-01 könnte für eine zweite Revision des ispLSI1016 stehen. Im LSI1024 finden sich an dieser Stelle die Zahlen 00.

Darunter sind relativ viele Masken abgebildet. Innerhalb der Schaltung kann man zwei Metalllagen identifizieren, die restlichen Schichten lassen sich nicht auflösen.

An den Kanten sind Überreste von Maskenkennzeichnungen und Teststrukturen zu erkennen, die sich in den Frässtraßen befanden.

SJDC steht für das San Jose Design Center, wo das Design wahrscheinlich entwickelt wurde.

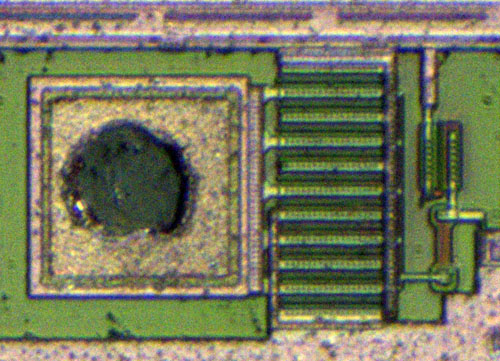

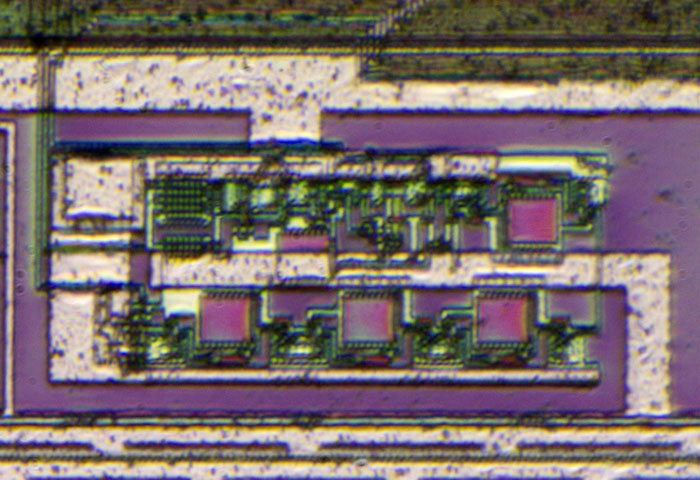

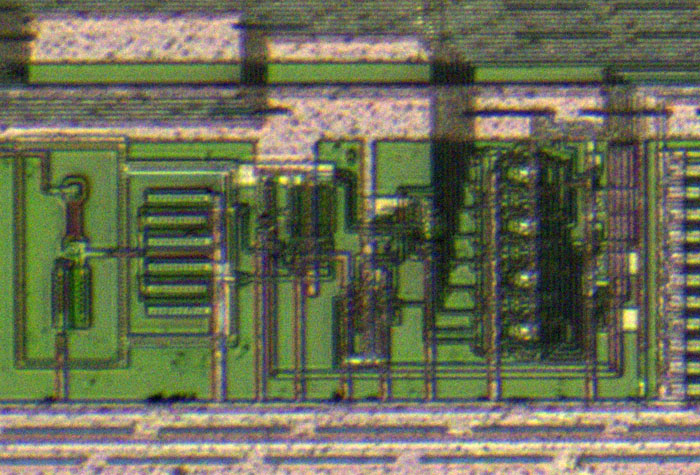

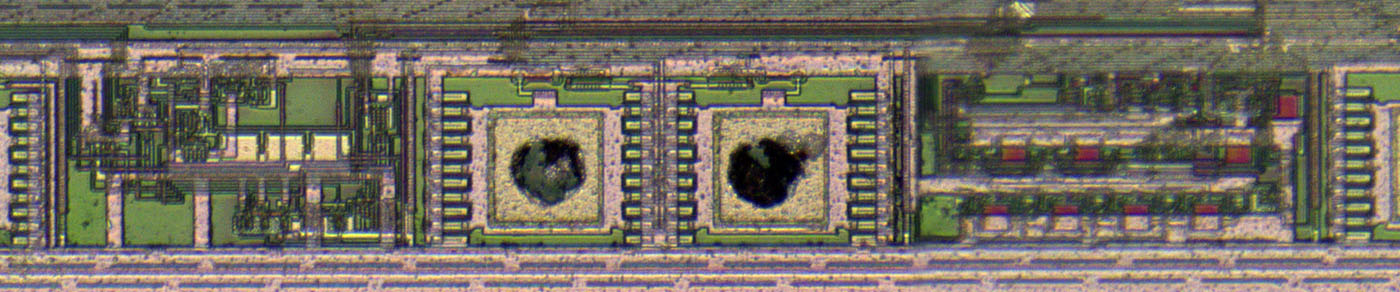

Die meisten Pins können als Ein- und Ausgänge konfiguriert werden. Vermutlich stellt der kleine Anschluss an der Oberseite des Bondpads den Eingangs-Pfad dar, während die größeren Strukturen rechts und links bei der Konfiguration als Ausgang Push/Pull-Transistoren darstellen.

Den wenigen Bondpads, die nur Eingänge darstellen, ist jeweils eine einzelne, größere Struktur zugeordnet. Die Struktur scheint an beide Versorgungspotentiale angebunden zu sein. Wahrscheinlich handelt es sich dabei um Clampingdioden, die Potentiale außerhalb des Versorgungsspannungsbereichs ableiten. Das hantelförmige Element dürfte ein Längswiderstand zum Schutz der folgenden Schaltungsteile sein. Darauf folgt unter anderem ein MOSFET, der höchstwahrscheinlich als Pull-Up- oder Pull-Down-Widerstand dient.

An der unteren Kante befindet sich ein Testpad, das während der Produktion kontaktiert wurde. Auffällig ist dabei, dass das Potential des Testpads nicht ins Innere des CPLDs geführt wird, sondern im äußersten Rand des Dies weitergeleitet wird.

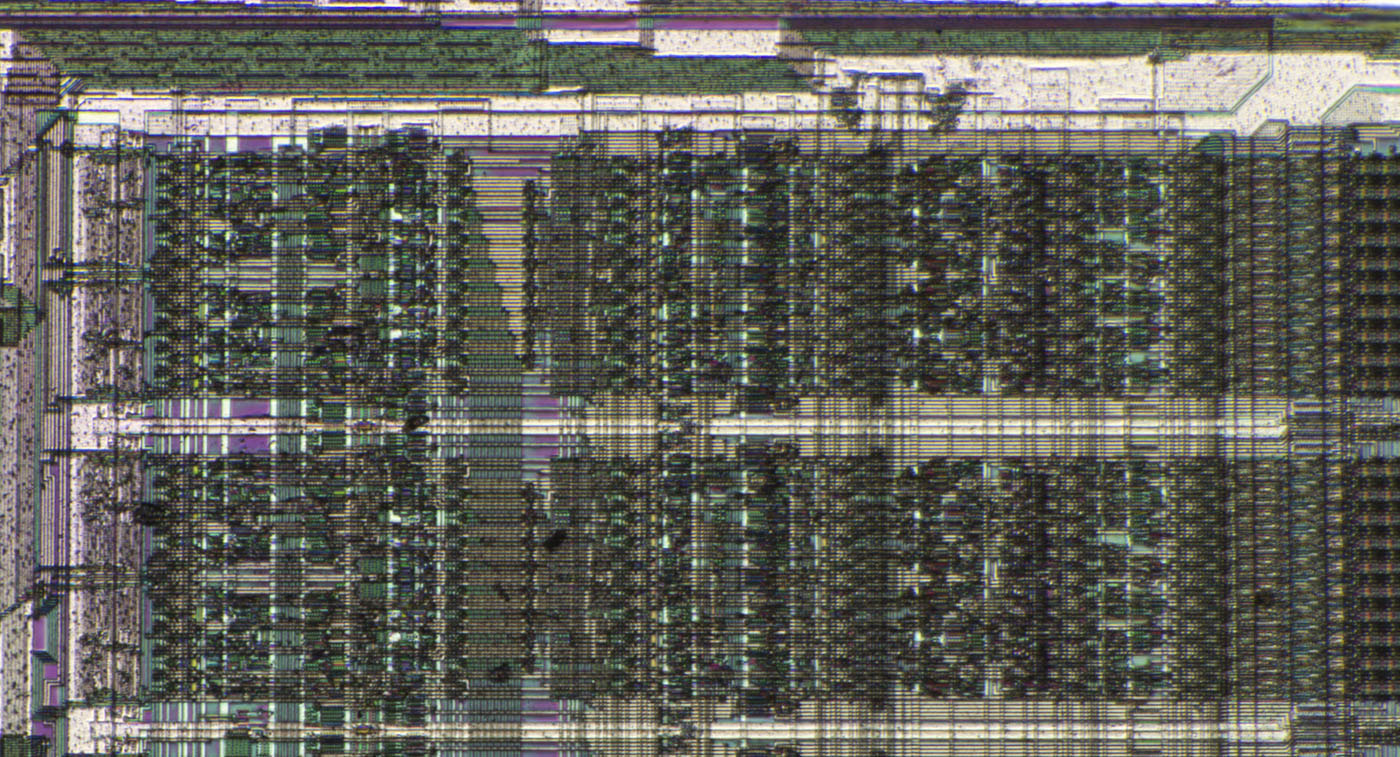

Die Strukturen sind etwas zu klein und die Funktionsblöcke zu hochintegriert, um die einzelnen Funktionen direkt identifizieren zu können. Gewisse Zusammenhänge lassen sich aber erkennen und auf andere kann man mit dem Wissen um die grundlegende Architektur zurückschließen.

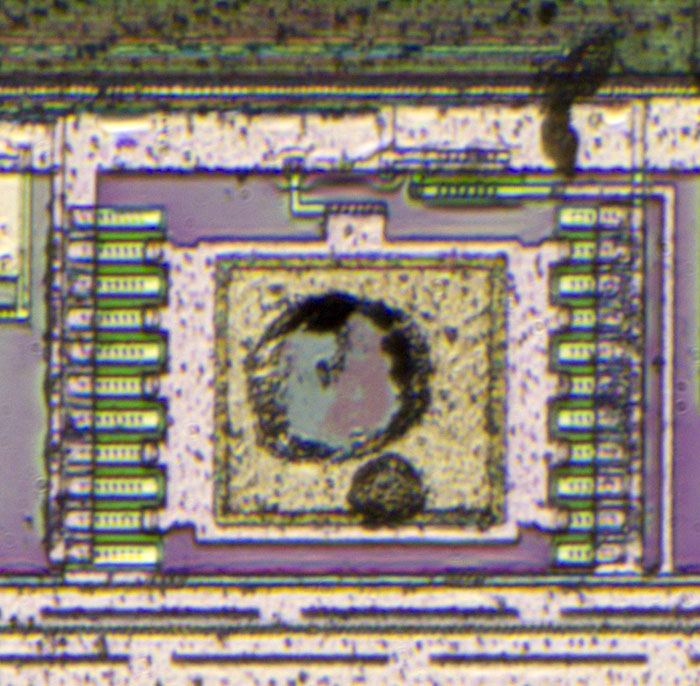

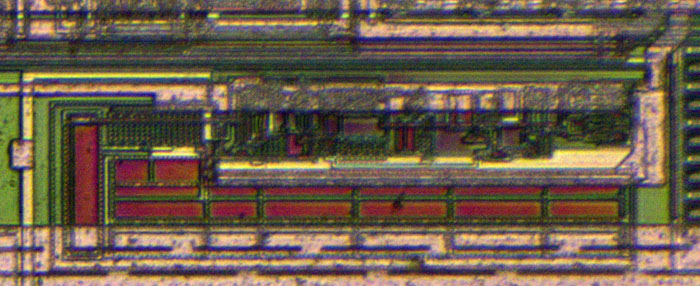

Rechts und links befinden sich die zwei Mega-Blöcke, die jeweils acht

Global-Logic-Blöcke enthalten (hellgrün/dunkelgrün). Entlang der Global-Logic-Blöcke

führt ein auffälliger Bus mit 16 Signalen (schwarz). Die 16 Leitungen stellen höchstwahrscheinlich die

Verbindungen des Output-Routing-Pools

dar. Dahinter dürften sich demnach die I/O-Zellen befinden (rot). Jeder rote

Block muss zwei I/O-Zellen beinhalten.

Zur Mitte hin

folgt auf den hellgrünen Teil eines jeden Global-Logic-Blocks das dunkelgrüne Logik-Array

über den sich die Eingangssignale des jeweiligen Blocks auswählen lassen. Im Gegensatz zu den

Output-Routing-Pools, die nur eine beschränkte Auswahl an Verbindungen

erlauben, ermöglicht das Logik-Array am Eingang der Global-Logic-Blöcke eine

beliebige Auswahl von 18x20 Verknüpfungen. Dementsprechend nimmt die

Schaltmatrix die große dunkelgrüne Fläche ein, während im Fall des

Output-Routing-Pools lediglich die

Busleitungen erkennbar sind.

Bei den großen Blöcken in der

Mitte des Dies (lila) handelt es sich um den Global-Routing-Pool. Darin können

laut Datenblatt alle Eingangssignale der Pins und alle Ausgangssignale der

Global-Logic-Blöcke zu den Eingängen der Global-Logic-Blöcke geleitet werden.

Um die einzelnen Funktionsblöcke sind diverse Rahmenstrukturen zu erkennen. Teilweise wird es sich um die Spannungsversorgung, teilweise um die Verteilung der Systemtakte handeln. Außerdem sind um den Umfang und durch die Mitte des Dies breite Leitungsgruppen verlegt, die diverse Strukturen kontaktieren (türkis).

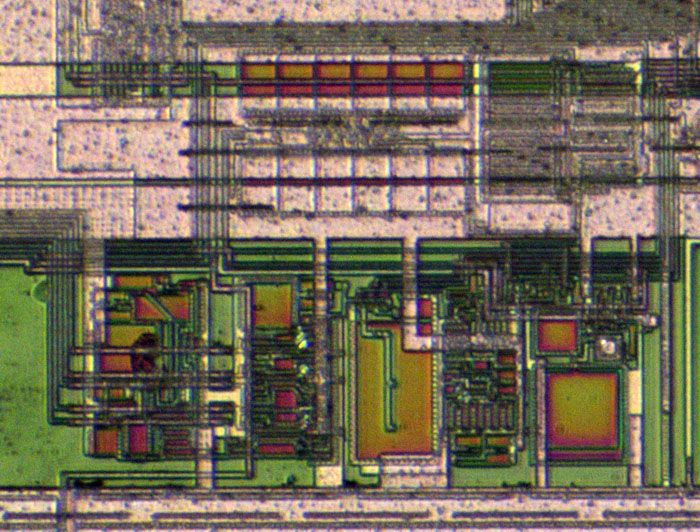

Zwischen den Bondpads befinden sich unterschiedliche Strukturen, deren Funktionen sich nicht bestimmen lassen. Es dürfte sich um diverse Hilfsschaltungen handeln, zum Beispiel zur Steuerung des Programmiervorgangs.

Neben dem CLK0-Bondpad ist ein Schaltungsblock platziert, der auf Grund seiner Verortung eine Taktaufbereitung darstellen könnte. Sicher ist das aber keineswegs.

An der rechten Kante befindet sich ein sehr regelmäßig strukturierter Schaltungsblock, der auf zwei Seiten vielfach kontaktiert wird. Der Aufbau erinnert an einen Speicherblock, es könnte sich aber auch um eine Art Multiplexer handeln, über den die vielen, verteilten Speicherzellen erreicht werden können.

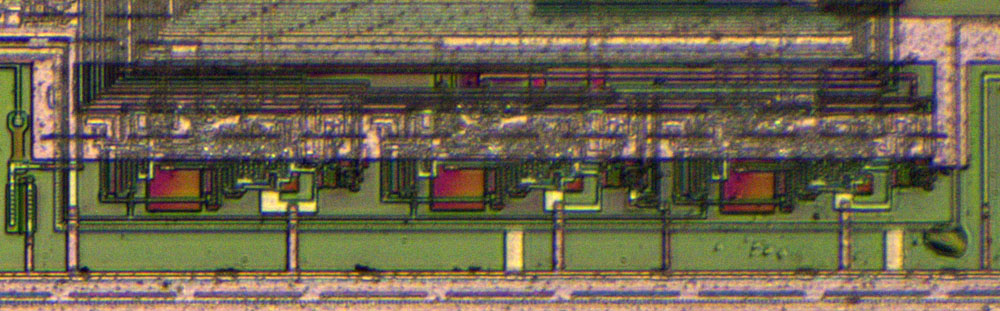

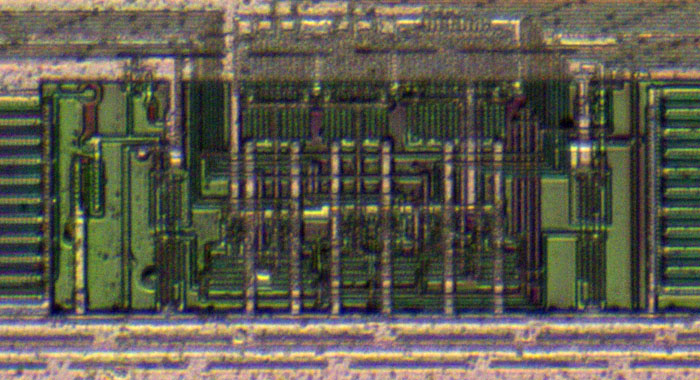

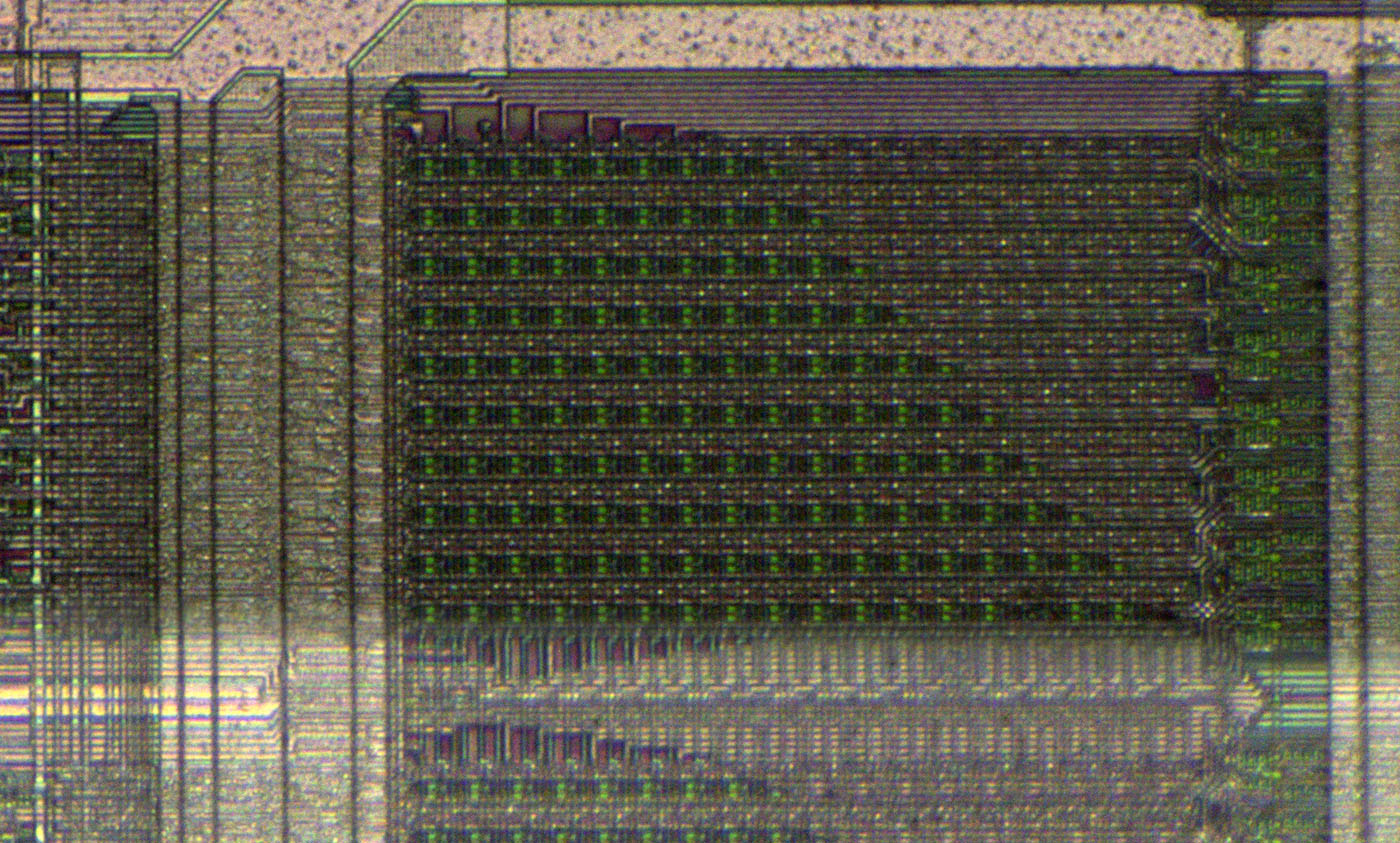

Die Details der Global-Logic-Blöcke lassen sich nicht identifizieren. Gut zu erkennen sind aber die 16 Leitungen des Output-Routing-Pools, die entlang der Global-Logic-Blöcke verlaufen und sie je nach Konfiguration mit den höchstwahrscheinlich daneben liegenden I/O-Zellen verbinden.

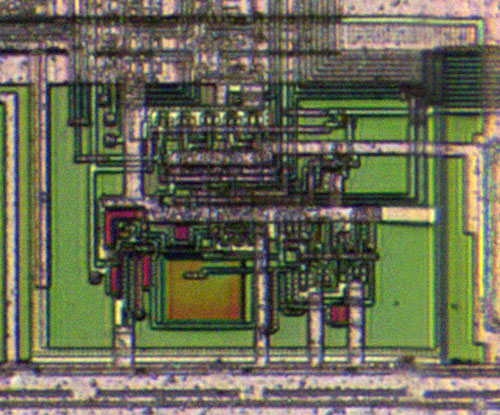

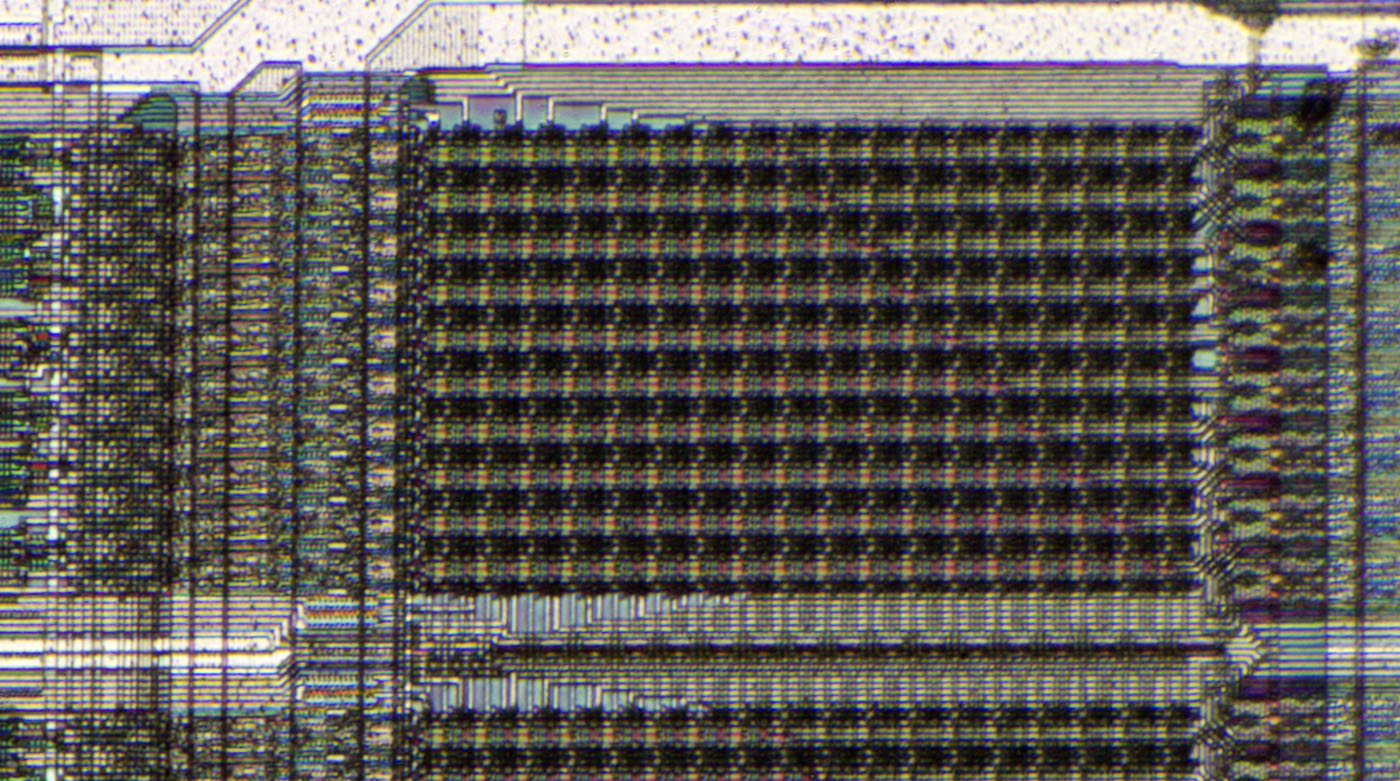

Die Verbindungsmatrizen der Global-Logic-Blöcke sind sehr hoch integriert, da sie 18x20 Signale miteinander verknüpfen und auch die dazu notwendigen Speicherzellen enthalten.

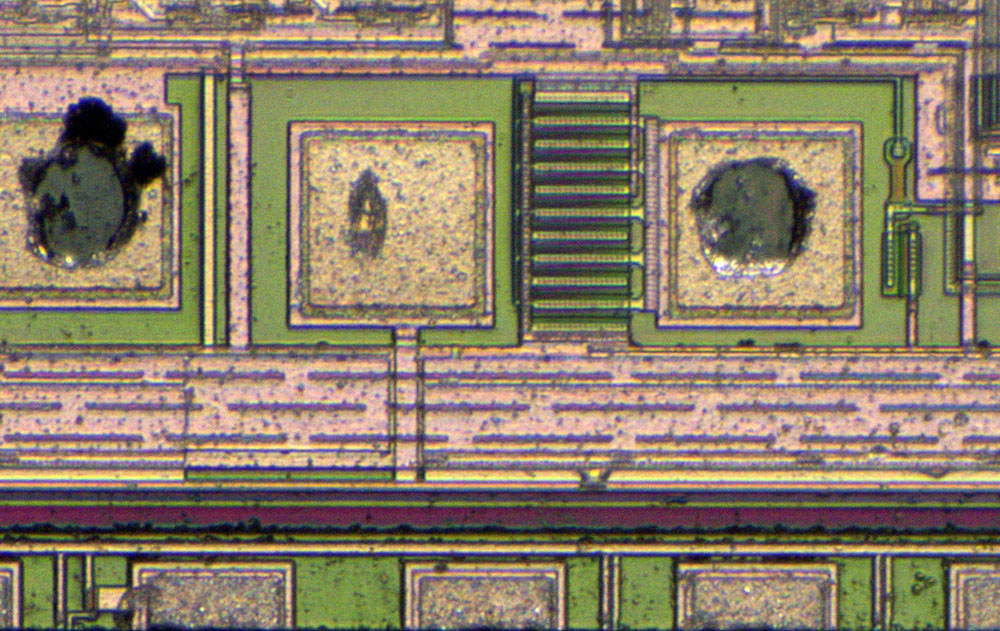

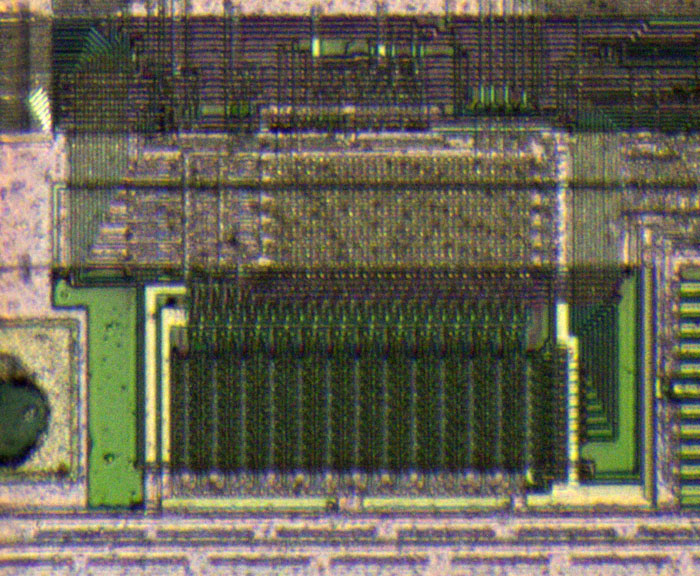

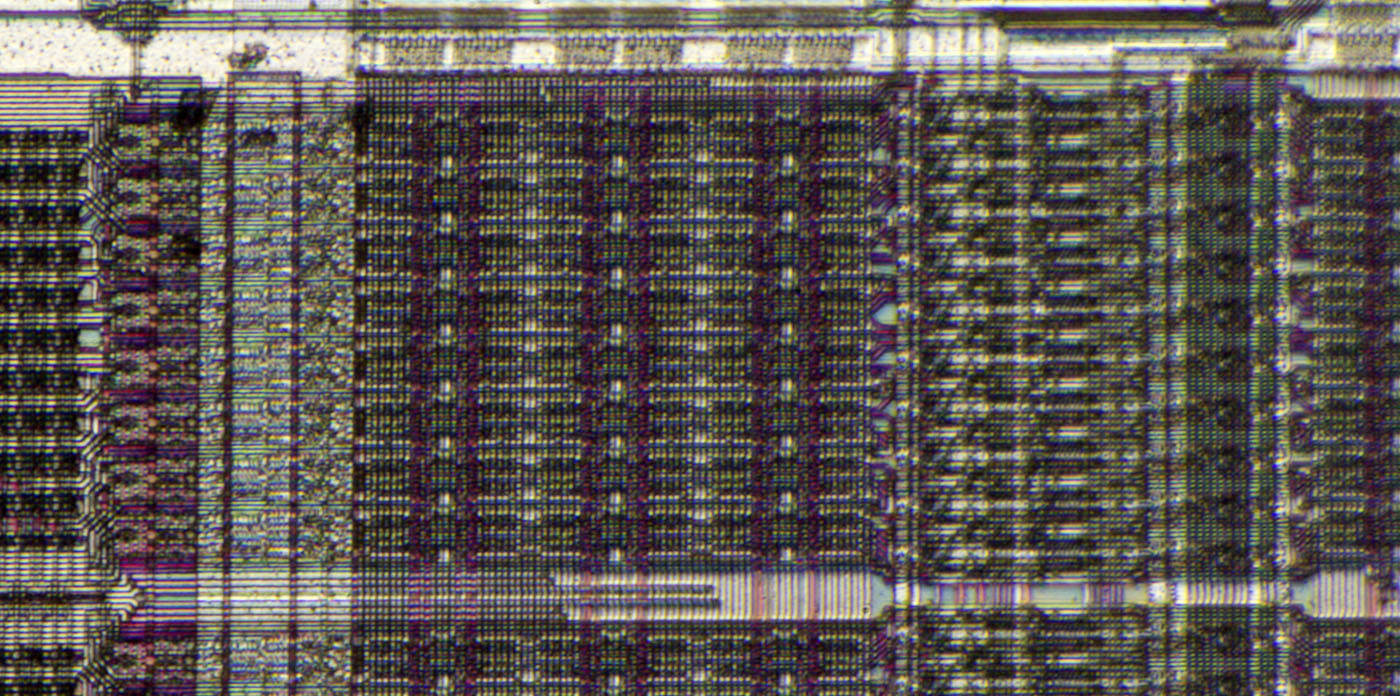

Der Global-Routing-Pool ist ebenfalls sehr hoch integriert. Den Strukturen nach besteht er in jeder Zeile aus drei Bereichen. Jedem Global-Logic-Block ist ein symmetrischer Schaltungsblock zugeordnet. Dazwischen befindet sich ein unsymmetrisch aufgebauter Schaltungsteil. Hier ist der linke der symmetrischen Blöcke und der mittlere, unsymmetrische Block abgebildet.

An der Oberseite sind unter der breiten Metallleitung mehrere Leitungsgruppen zu erkennen. Höchstwahrscheinlich handelt es sich um die Eingangssignale der I/O-Zellen und die Ausgangssignale der Global-Logic-Blöcke, die über den Global-Routing-Pool mit den Eingängen der Global-Logic-Blöcke verbunden werden können.