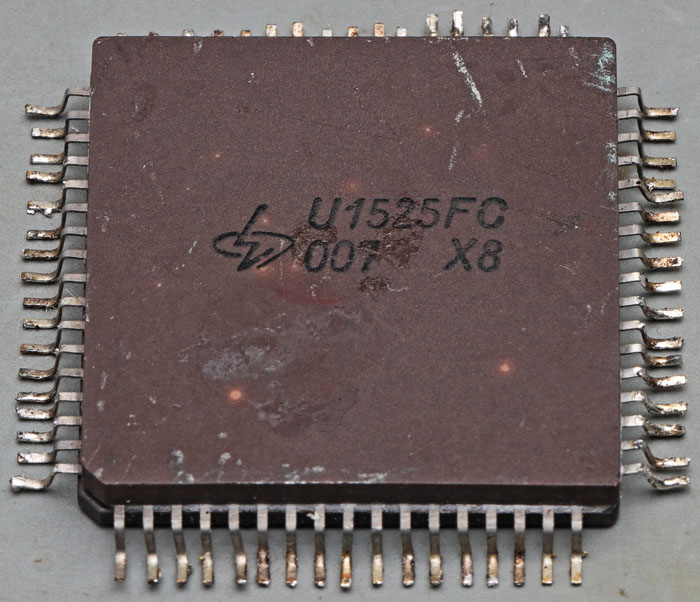

Der U1525FC007 ist ein Standardzellen-ASIC, der im Bildungscomputer Robotron A5105 eingesetzt wurde. In diesem Teil der Dokumentation werden anhand dieses Bausteins lediglich der Aufbau und die Eigenschaften des zugrunde liegenden Standardzellen-Entwurfsystems U1520 betrachtet. Eine genauere Analyse der Funktionen des U1525FC007 erfolgt im dritten und vierten Teil der Dokumentation. Die Zeichen X8 stehen für eine Fertigung im August 1989.

Die Grundlage des U1525FC007 ist das Standardzellensystem U1520. Dabei handelt es sich um eine Entwicklung aus dem Zentrum für Mikroelektronik Dresden, das später zum Kombinat Carl Zeiss Jena gehörte. Neben dem U1520-Standardzellensystem hatte man das U1500-Standardzellensystem und die U5200-Gatearrays im Programm. Viele Informationen zu allen drei Systemen finden sich in dem Dokument "Applikative Informationen 4/88" herausgegeben vom VEB Applikationszentrum Elektronik Berlin.

Jede der drei Architekturen hat Vor- und Nachteile. Einfache Gatearrays wie das U5200-System beinhalten eine feste Anordnung von einfachen Gattern und Flip-Flops. Komplexere Logikblöcke werden mit Kombinationen der verfügbaren Gatter dargestellt. Zur Implementierung der gewünschten Funktionen werden lediglich die Verdrahtungsebenen anwendungsspezifisch strukturiert. Dadurch können die sogenannten Master mit dem immer gleichen Maskensatz produziert werden und es bleiben nur noch wenige anwendungsspezifische Masken. Im Fall des U5200 sind es 3 Masken.

Baut man eine Schaltung mit Standardzellen-ASICs wie dem U1500 oder dem U1520 auf, so kann man auf verhältnismäßig viele unterschiedliche Standardzellen zurückgreifen. Diese Gatter und Flip-Flops haben eine spezifische, optimierte Struktur. Sie benötigen dadurch weniger Fläche und haben üblicherweise ein besseres dynamisches Verhalten. Außerdem kann man exakt die Anzahl der jeweiligen Elemente auswählen, die man benötigt und sie sehr frei anordnen. Die Entwicklung eines solchen ASICs wird dadurch aber auch aufwändiger. Auch die Produktion ist aufwändiger, weil alle Masken anwendungsspezifisch sind. Im Fall des U1500 sind es 9 Masken. Im Fall des U1525 sind es 12 Masken. Allen Architekturen ist gemeinsam, dass ein Großteil der Strukturen erprobt ist. Das vereinfacht die Umsetzung einer anwendungsspezifischen Schaltung.

Das System U1500/U1520 bietet über 40 verschiedene Standardzellen und ermöglicht die Integration von bis zu 13.000 Transistoren. Im Jahr 1988 werden 30-300 Ostmark als Preisrahmen angegeben. "Ökonomisch günstige Stückzahlen" wären demnach 1.000 - 100.000 pro Jahr. Für das U5200 Gatearraysystem findet sich dagegen eine "ökonomische Obergrenze" von 10.000 Stück pro Jahr.

Die Standardzellen-ASICs U1500 und U1520 basieren auf dem Prozess CSGT2. CSGT steht für "Complementary Silicon Gate Technology". Es handelt sich um einen 5V-CMOS-Prozess, mit einer minimalen Strukturgröße von 4µm. Der Arbeitstakt des Prozesses beträgt typischerweise 4MHz, die Gatterlaufzeit wird mit 5ns angegeben. Für den U1500 und den U1520 kamen zwei unterschiedliche Varianten des CSGT2-Prozesses zum Einsatz. Der U1500 basiert auf dem Prozess CSGT2/N, der U1520 auf dem Prozess CSGT2/S. Die dynamischen Parameter der zwei Prozesse sind zwar unterschiedlich, es heißt aber, dass man diesbezüglich keinen Prozess als besser bezeichnen könne. Der CSGT2/S erlaubt lediglich höhere Packungsdichten, weil die Standardzellen kleiner sind. Dafür ist der Herstellungsprozess aufwändiger.

Die Nachfolgegenerationen von U1500 und U5200 waren die Systeme U1600 und U5300, deren minimale Strukturbreite nur noch 1,5µm beträgt und die zwei Metalllagen besitzen. Mit noch etwas größeren Chipflächen steigt die maximal mögliche Transistoranzahl auf bis zu 100.000 Stück. Die Arbeitsfrequenz steigt auf 25MHz, die Gatterlaufzeit sinkt auf maximal 1,6ns. Im U1600-System waren dann auch RAM-, ROM- und PLA-Bereiche verfügbar.

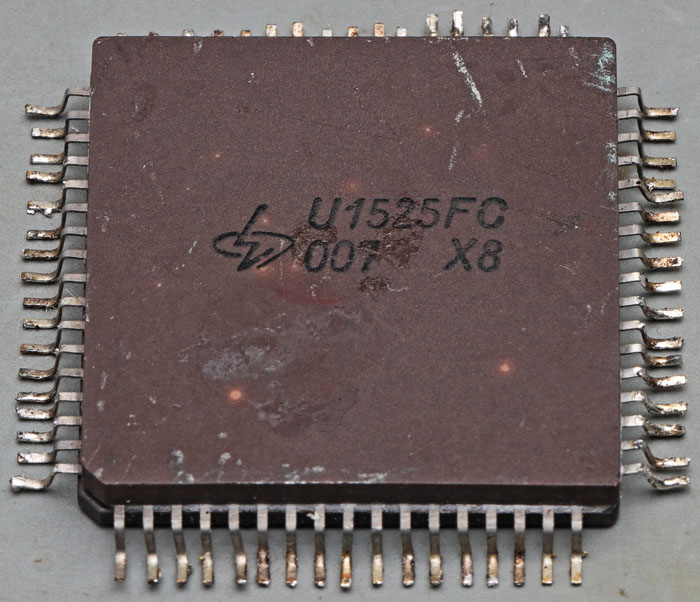

Etwas früher, in dem Dokument "Applikative Informationen 3/88" findet sich eine Gegenüberstellung, die die Vor- und Nachteile der verschiedenen Produktfamilien gegenüberstellt.

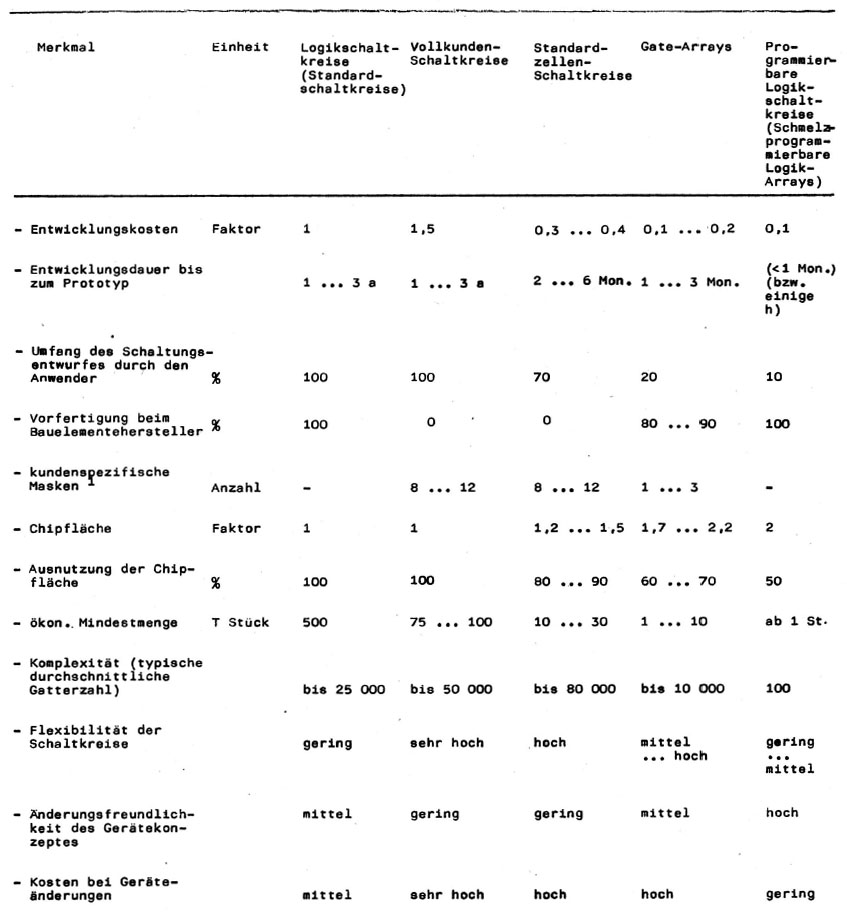

Im obigen Bild sind die sinnvollen Einsatzbereiche noch etwas einfacher dargestellt. Standardzellen-ASICs wurden vor allem bei mittleren Stückzahlen als sinnvoll angesehen. Zu komplexeren Schaltungen hin erweitert sich der Einsatzbereich.

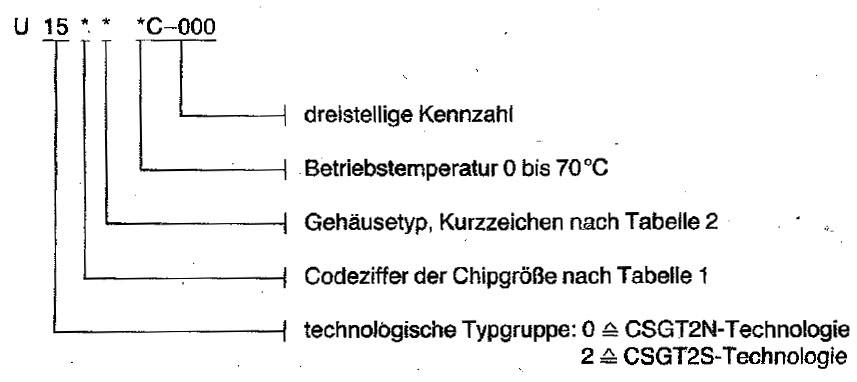

Der Fachbereichsstandard TGL 43876 beschreibt wie die Standardzellen-ASICs U1500/U1520 beschriftet wurden. Die Zuordnung der Beschreibung zu den Zeichen ist aber leider etwas verschoben. Die Bezeichnung U1525FC007 erklärt sich folgendermaßen: U15 steht für diese Generation der Standardzellen-ASICs. Die 2 zeigt, dass der Baustein mit dem CSGT2/S-Prozess gefertigt wurde. Die Zahl 5 steht für die maximale Chipgröße mit einer Kantenlänge von 7,5mm. F gibt an, dass es sich um ein Keramikgehäuse handelt. Der Buchstabe C zeigt den üblichen Betriebstemperaturbereich. 007 ist schließlich die spezifische Typbezeichnung des ASIC-Designs.

In der Tabelle 2 des Fachbereichstandards sieht man welche Chipgrößen im Rahmen des U1500/U1525-Systems verfügbar waren und in welchen Gehäusetypen diese bezogen werden konnten.

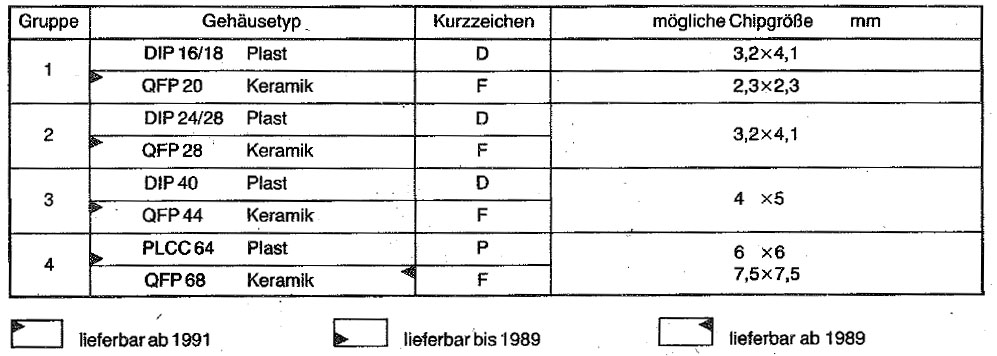

Das Keramikgehäuse lässt sich leicht öffnen.

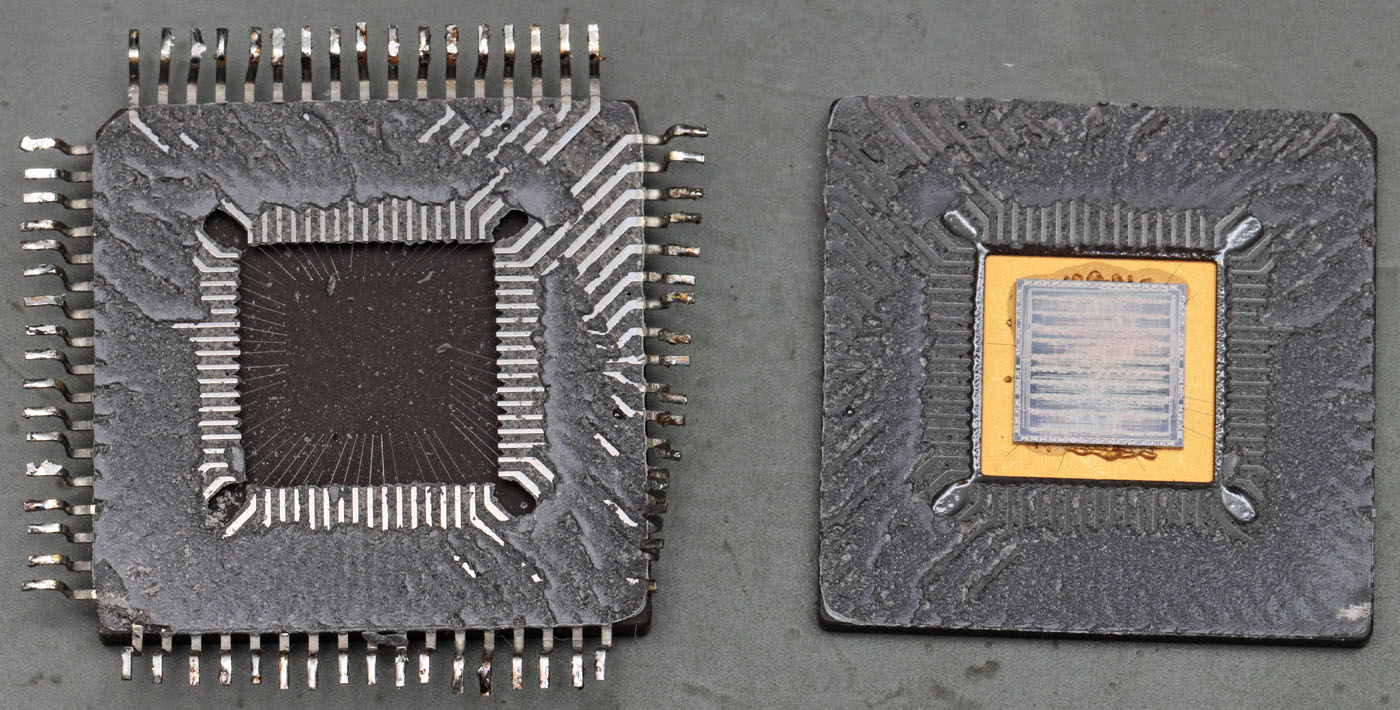

Das obige Bild zeigt das Die des U1525FC007 und ist in Originalgröße (34MB) verfügbar.

![]()

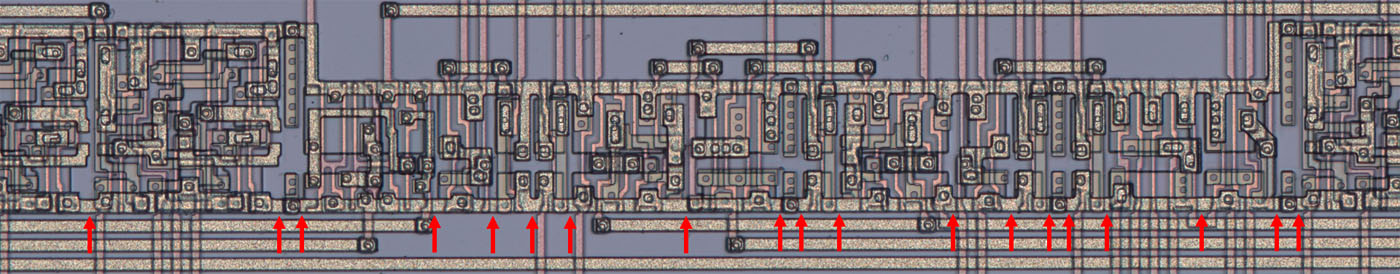

Auf dem Die finden sich keinerlei Beschriftungen oder Symbole. Lediglich an der unteren Kante sind in den Überresten der Frässtraße Beschriftungen von Hilfsstrukturen zu erkennen.

Der Aufbau des U1525FC007 ist typisch für eine Standardzellen-Architektur. Die aktiven Elemente sind in Zeilen aufgereiht. Die Verbindung der Zellen erfolgt zwischen den Zeilen über eine Polysiliziumlage für vertikale Leitungen und innerhalb einer Metalllage für horizontale Leitungen. Seitlich wird die Versorgungsspannung zugeführt. Müssen weiter voneinander entfernte Schaltungsteile miteinander verbunden werden, kann der Bereich zwischen den Standardzellen-Zeilen und dem Bondrahmen genutzt werden. Dort verlaufen auch die Leitungen zwischen den Schnittstellen im Bondrahmen und den inneren Schaltungsteilen.

Die Abstände zwischen den Logikzeilen sind nicht immer gleich. Man hatte bei den Standardzellen-ASICs aber anscheinend noch deutlich mehr Freiheiten. Im U1500PC050 sind die Schaltungsteile viel individueller angeordnet und wurden mit sehr speziellen Strukturen ergänzt.

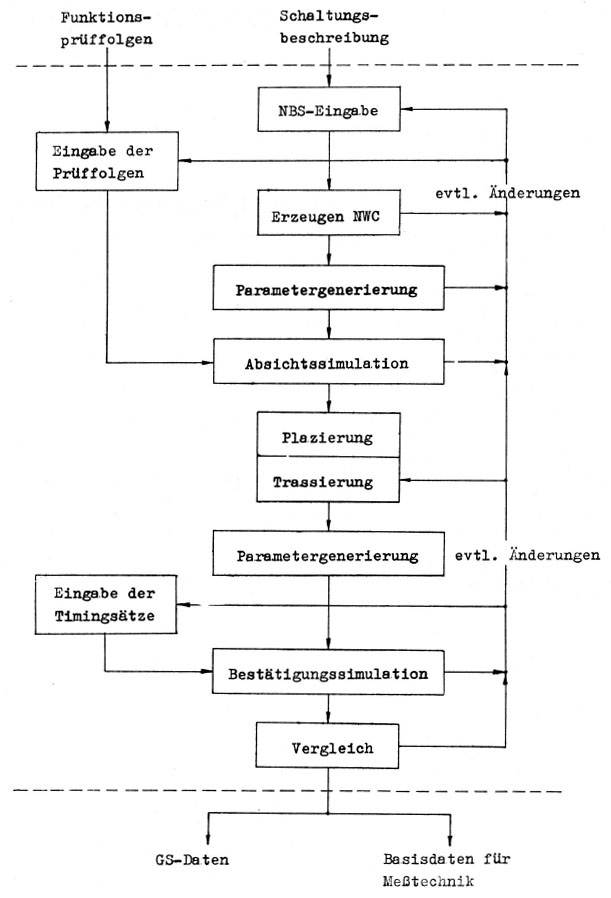

Das Dokument "Applikative Informationen 4/88" beschreibt, wie Standardzellen-ASICs entwickelt wurden. Hat der Anwender seine Logikschaltung definiert, so kann man die Platzierung und die Verbindung der Zellen automatisiert umsetzen lassen.

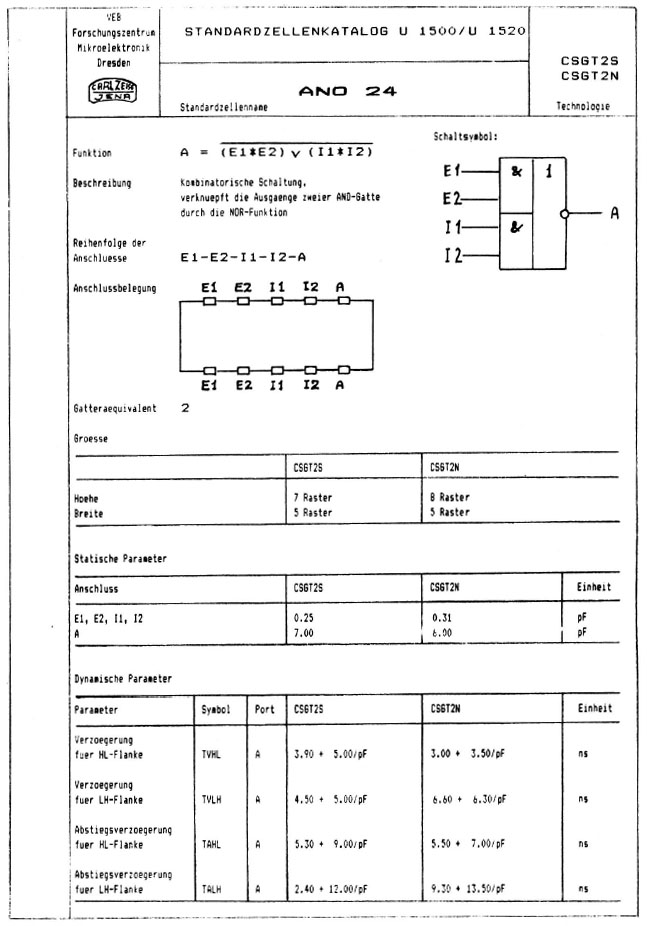

Den "Applikative Informationen 4/88" nach kann man im U1500/U1520-System aus einem Katalog von 43 Standardzellen wählen. Dazu existiert ein Standardzellenkatalog, aus dem eine Seite abgebildet ist. Der vollständige Katalog ist leider nicht öffentlich verfügbar.

Jede Standardzelle hat einen Namen, hier "ANO 24". In der oberen rechten Ecke sieht man, in welchem Prozess diese Zelle verfügbar ist. Darunter findet sich das zugehörige Symbol, die mathematische Beschreibung und eine textuelle Beschreibung des Verhaltens. Beim Entwurf des Layouts sind die Standardzellen durch Rechtecke mit dem jeweiligen Symbol dargestellt. Das gesamte Layout ist in Raster eingeteilt. Die hier zu sehende Standardzelle nimmt 7x5 beziehungsweise 8x5 Rasterzellen ein. Die Beschreibung der Zelle zeigt welche Schnittstellen an der oberen und unteren Kante vorhanden sind.

Das Gatterequivalent ermöglicht es den voraussichtlichen Flächenbedarf der Schaltung abzuschätzen. Ein Gatter wird dabei mit vier Transistoren angenommen. Das ANO 24 Gatter benötigt entsprechend die Fläche von acht Transistoren.

Im unteren Bereich finden sich schließlich noch die parasitären Kapazitäten der Eingänge und die zulässige kapazitive Belastung des Ausgangs. Mit diesen Zahlen ergibt sich die maximal zulässige Anzahl an Gattern, die an einen Ausgang angeschlossen werden dürfen. Leitungskapazitäten sind zusätzlich zu addieren. Die Werte gelten für die typische Arbeitsfrequenz von 4MHz, bei geringeren Frequenzen dürfen mehr Gatter mit einem Ausgang verbunden werden. Die Obergrenze sind 50 Gatter. Unter den zulässigen Kapazitäten sind außerdem die Verzögerungszeiten des jeweiligen Gatters definiert.

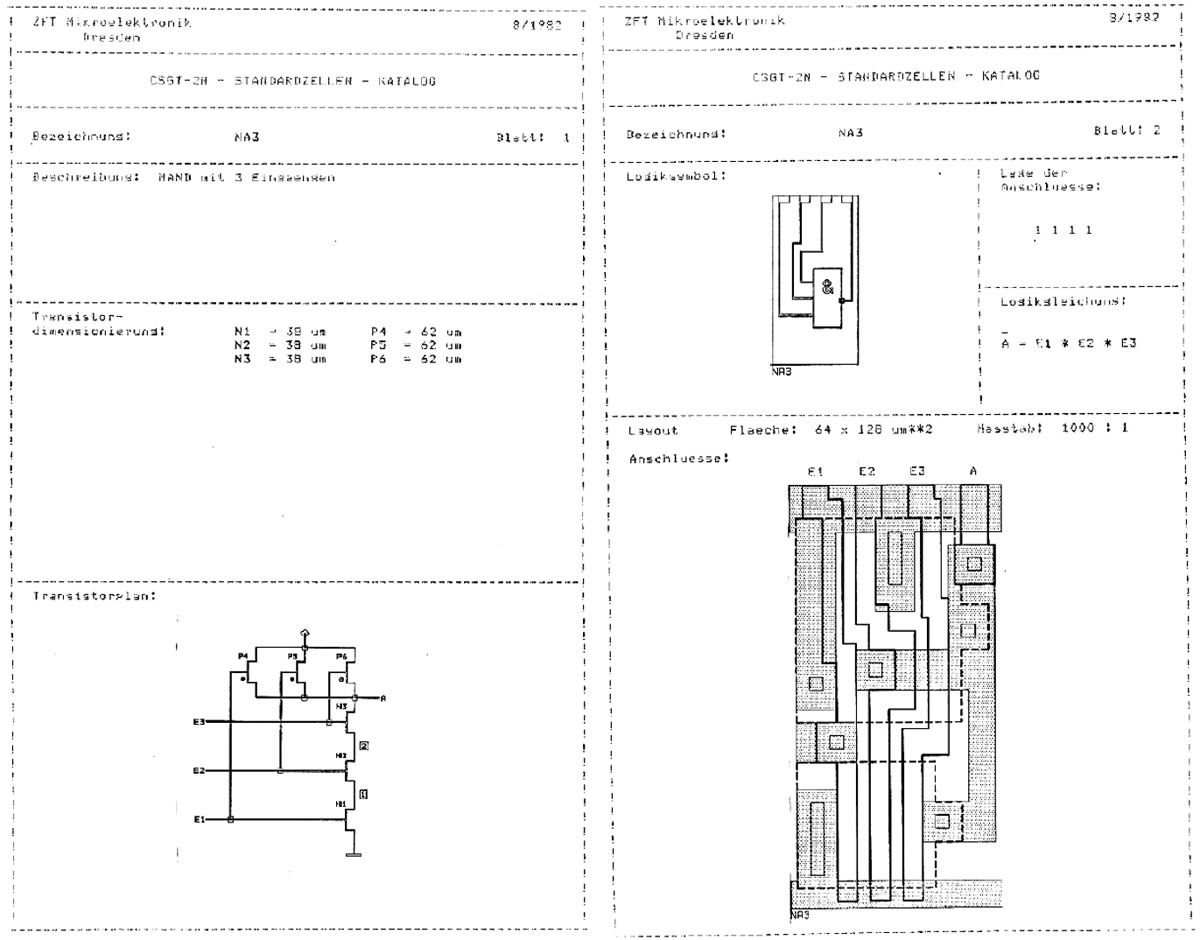

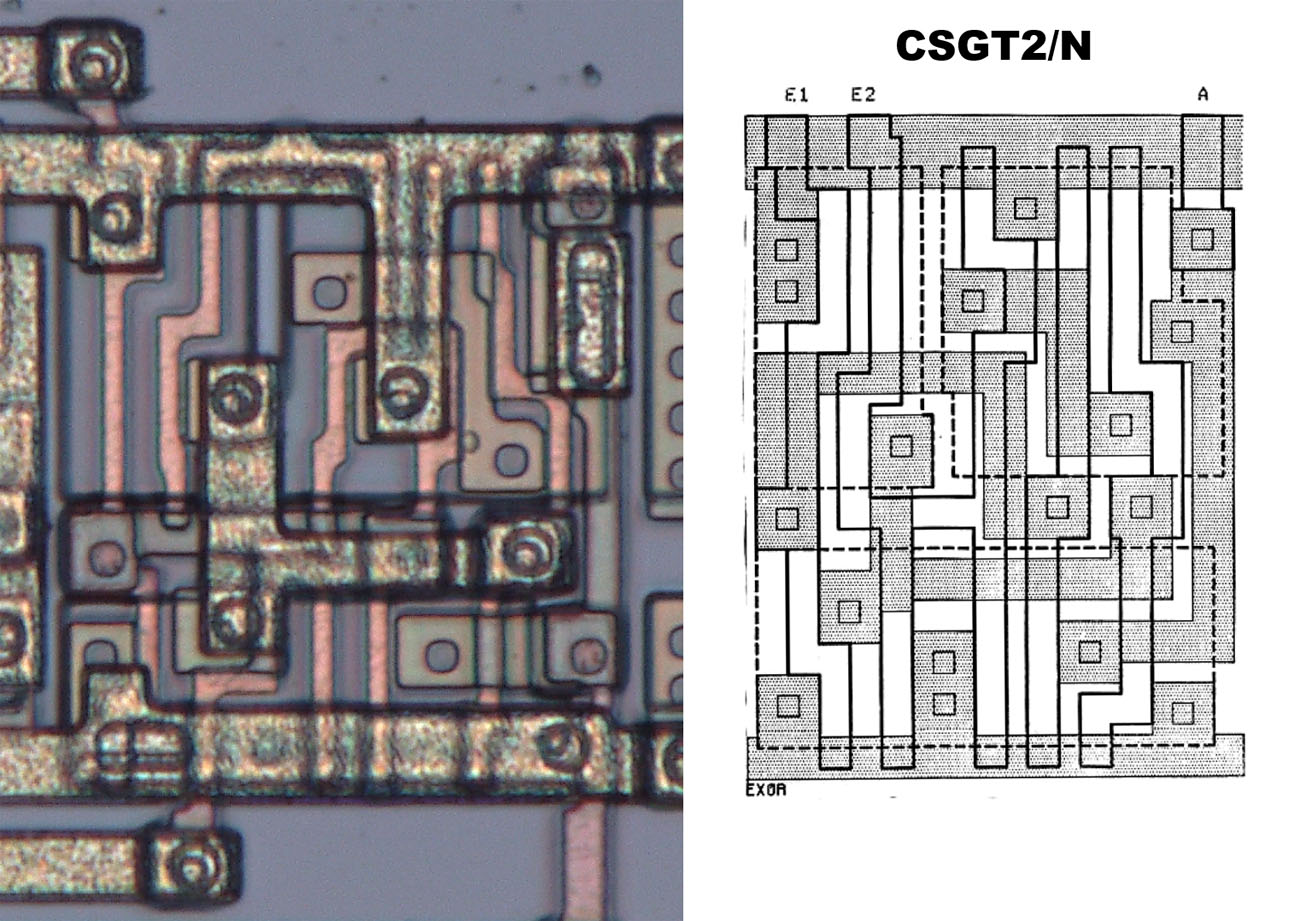

Auf der Webseite von Dr. G. Heinz ist ein früher Standardzellenkatalog aus dem Jahr 1983 öffentlich verfügbar. Dieser Katalog dokumentiert allerdings lediglich die Möglichkeiten der U1500-ASICs, die auf dem CSGT2/N-Prozess basieren: http://www.gheinz.de/publications/berliner_ics/index.htm#35

Die Beschreibung der Zellen ist teilweise noch etwas ausführlicher. Auf der ersten Seite findet sich sowohl ein Schaltplan als auch die Gatebreite der Transistoren. Auf der zweiten Seite sind die zugehörigen Strukturen abgebildet, wie man sie auf dem Die findet.

In diesem Dokument steht außerdem, dass es möglich war neue Standardzellen zu definieren. Die neuen Zellen sind dann mit den Herausgebern abzustimmen.

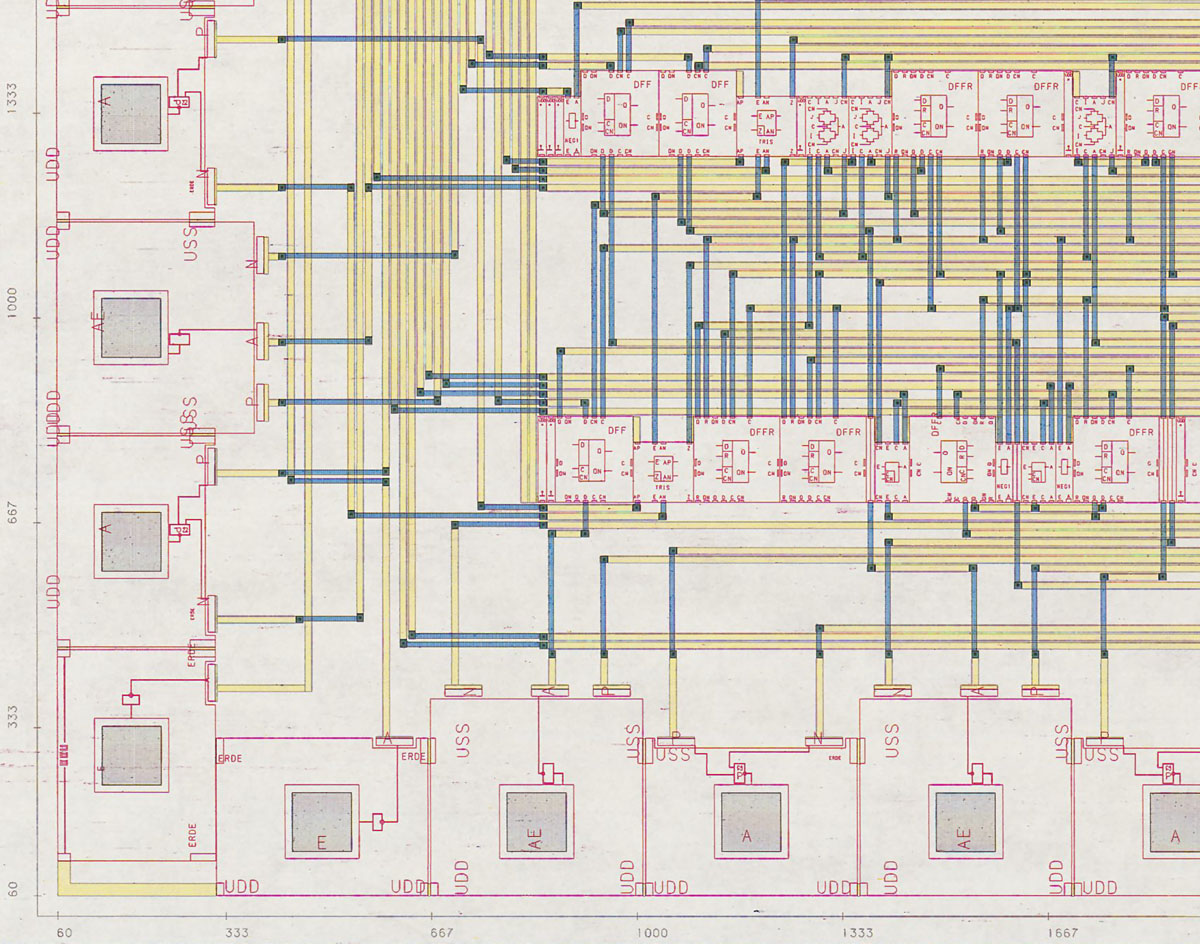

Auf der Webseite von Dr. G. Heinz findet man die Layoutdaten des U1520PC201, einer anderen U1520-Variante: http://www.gheinz.de/publications/berliner_ics/index.htm#slic-b

Die Standardzellen sind als Rechtecke mit den zugehörigen Symbolen dargestellt. An den oberen und unteren Kanten findet man die beschrifteten Ein- und Ausgänge. Die Elemente sind unterschiedlich breit. Flip-Flops sind etwas höher als gewöhnliche Gatter. Im Bondrahmen befinden sich die notwendigen Ein- und Ausgangsblöcke. Dazwischen sorgen Leitungen in der Polysiliziumlage und in der Metalllage für die notwendigen Verbindungen.

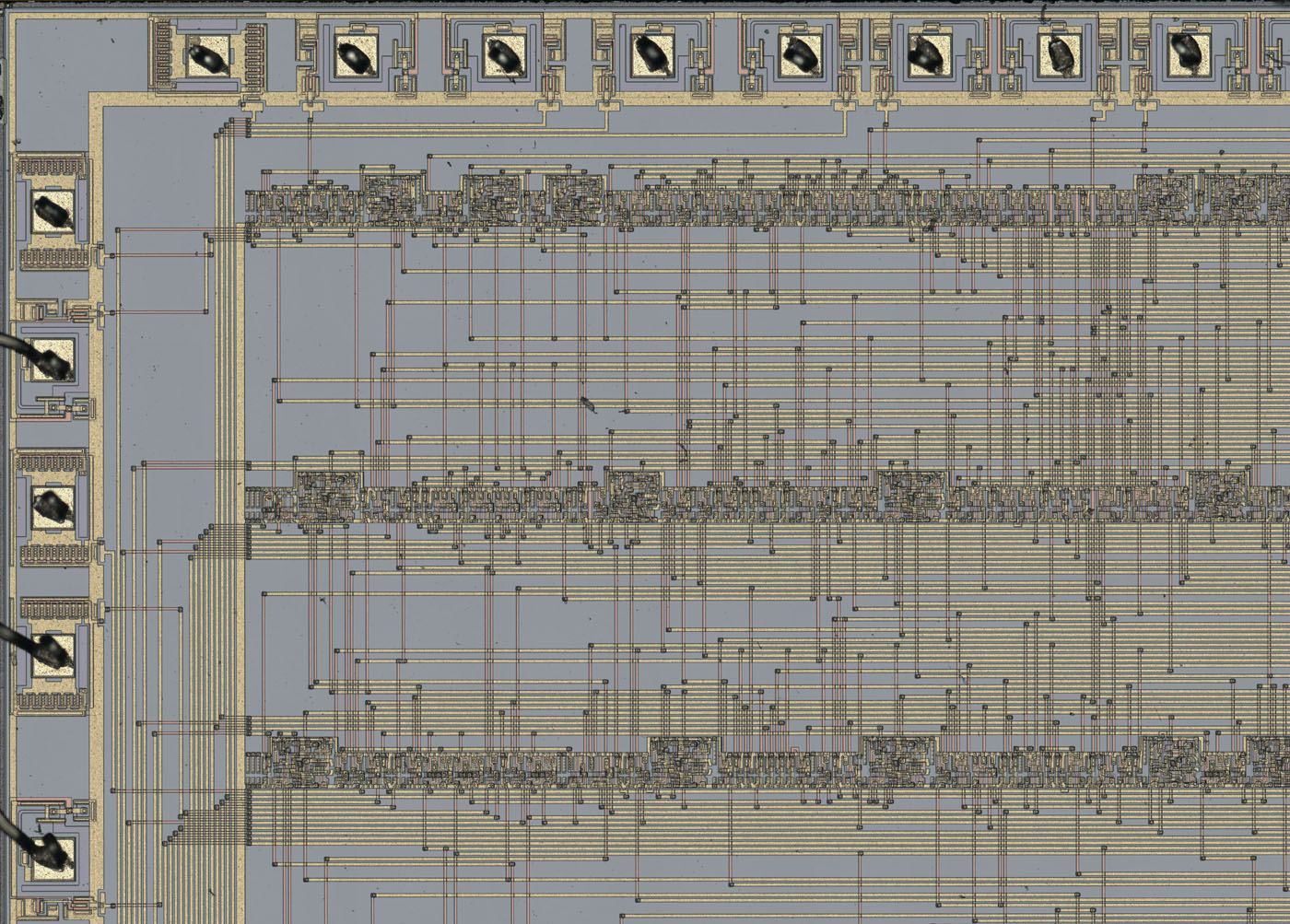

In der realen Schaltung sind die Zellen deutlich schlechter auszumachen, mit etwas Übung kann man die Übergänge von einer zu nächsten Zelle aber gut erkennen.

Der Standardzellenkatalog liegt nur für den CSGT2/N-Prozess vor. Zwar bietet der CSGT2/S-Prozess fast die gleichen Standardzellen, die Strukturen sind aber deutlich unterschiedlich. Weiß man welche Zellen man gegenüberstellen muss, so kann man im direkten Vergleich einige Gemeinsamkeiten erkennen. Für eine einfache Identifikation der Zellen reicht es aber nicht. Aus diesem Grund ist es notwendig die Funktion jeder einzelnen Zelle zu verstehen. Das Wissen über die grundlegende Technik und die vorhandenen Logikblöcke ist dabei aber sehr hilfreich.

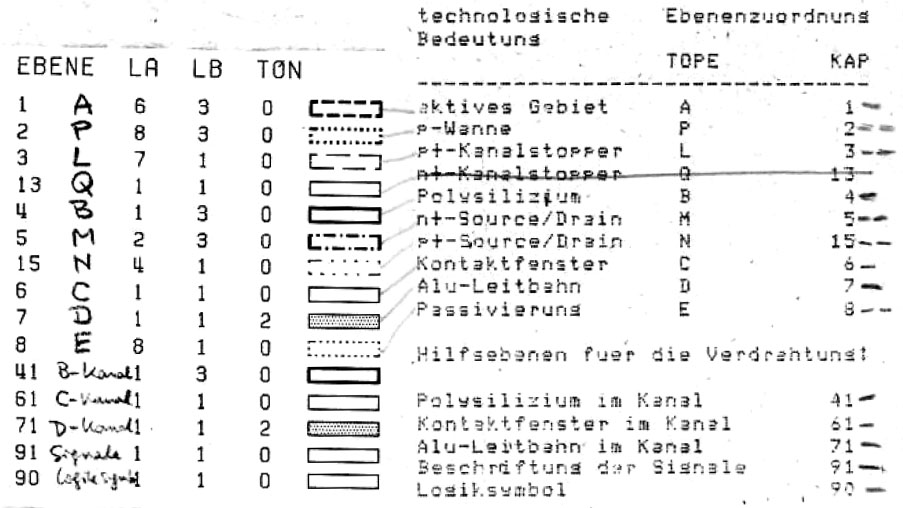

Im CSGT2/N-Standardzellenkatalog sind die verwendeten Masken abgebildet. Es sind 10 Masken aufgeführt, der n+-Kanalstopper war aber nicht notwendig, wie Dr. G. Heinz 1985 ausführlich erklärt: http://www.gheinz.de/publications/berliner_ics/index.htm#18

So ergeben sich die bereits beschriebenen 9 Masken eines relativ einfachen CMOS-Prozesses. Bei der Betrachtung der Gatter fällt sofort auf, dass der U1520 komplexer ist. Man erkennt eine zweite Polysiliziumlage. Dem U1520-System werden 12 Masken zugeschrieben. Eine Maske strukturiert die zweite Polysiliziumlage. Die anderen beiden Masken könnten für unterschiedliche Kontakte genutzt worden sein, nämlich zur ersten Polysiliziumlage und zum Substrat. Derart differenzierte Kontaktmöglichkeiten sind aber eigentlich unüblich.

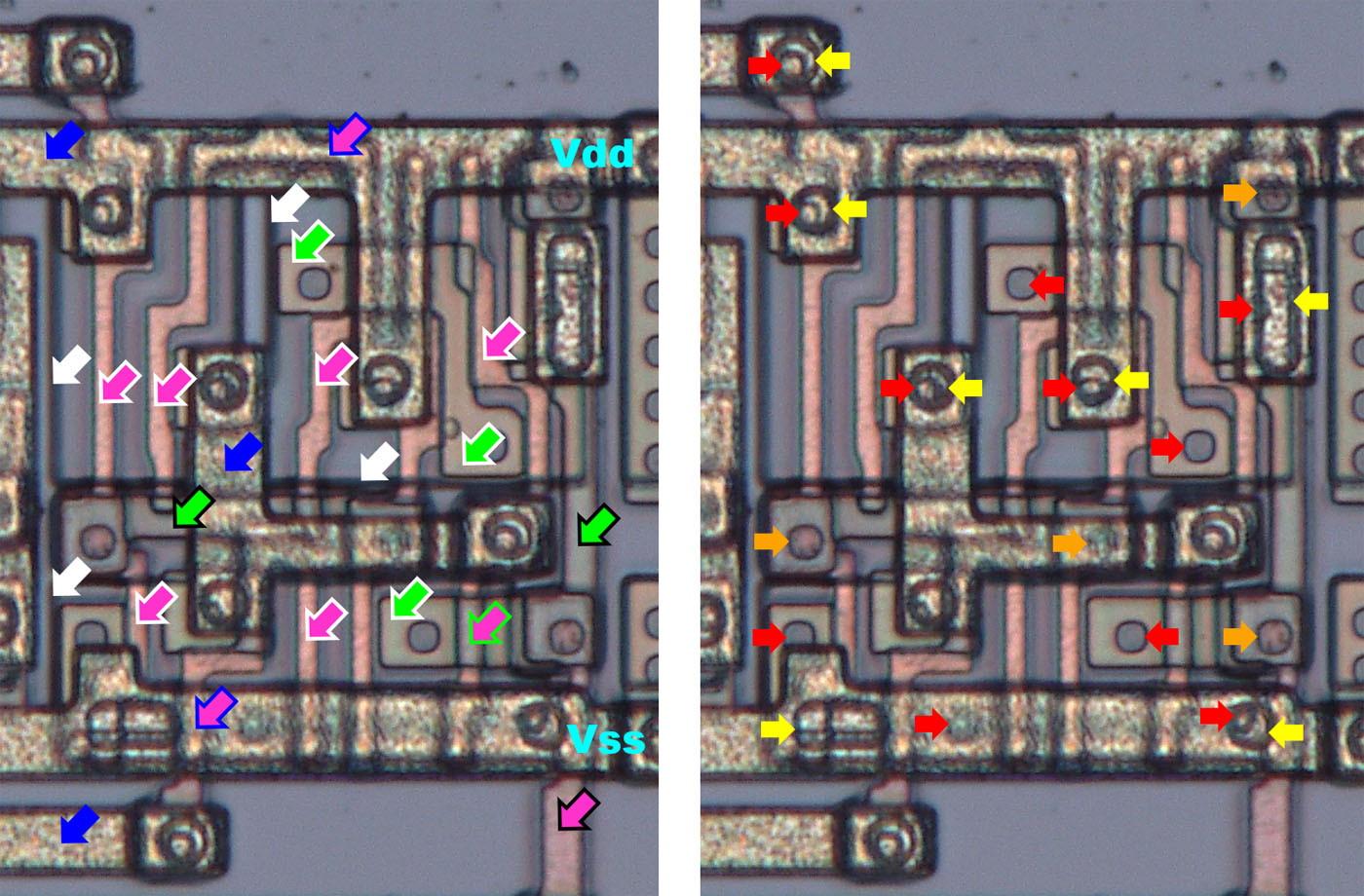

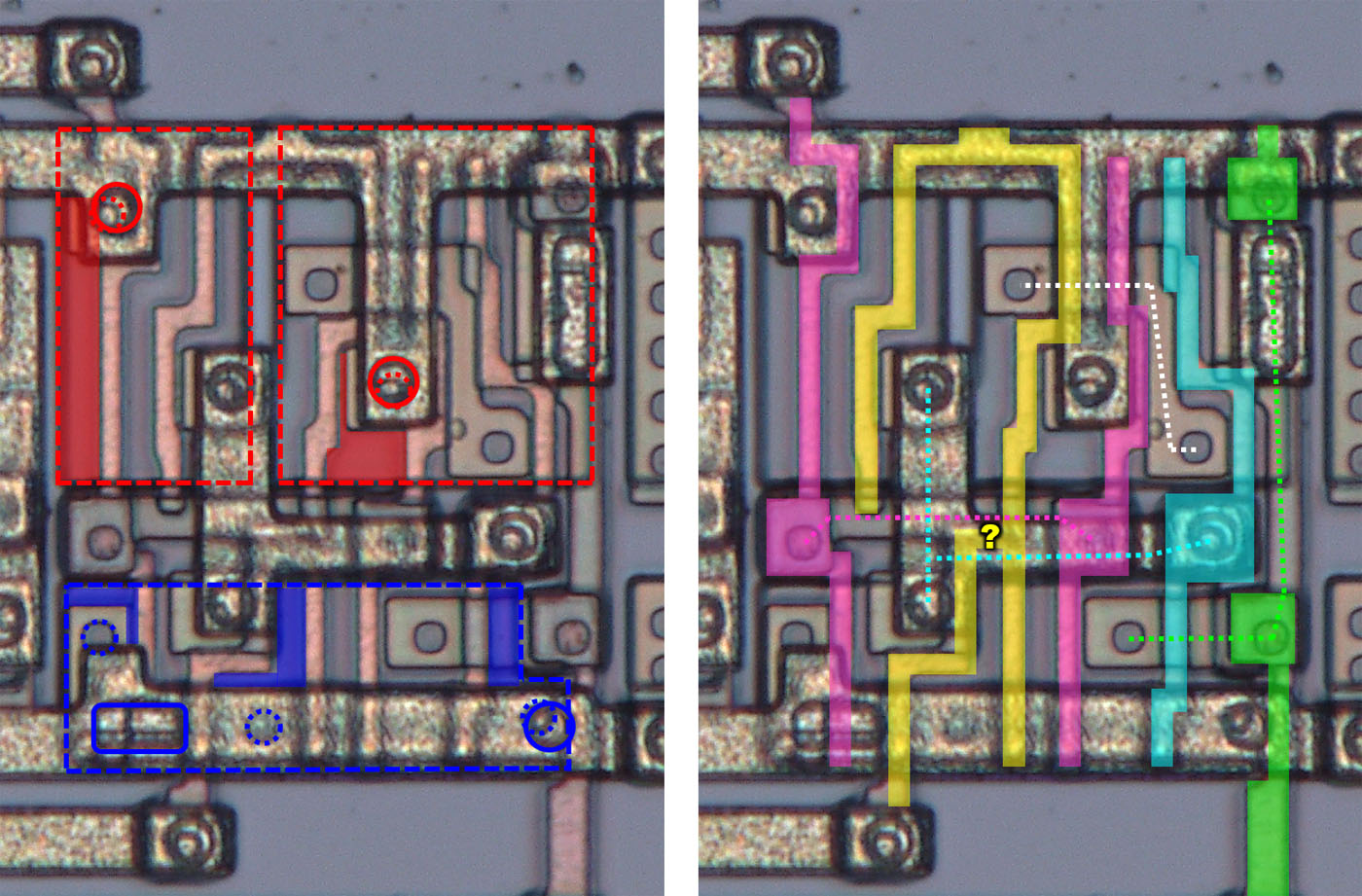

Oberhalb und unterhalb der Logikzeilen befinden sich in der Metalllage die Versorgungsleitungen. Die Metalllage (blau) dient hauptsächlich der Stromversorgung und der Signalweiterleitung zwischen den Standardzellen. Sie wird aber teilweise auch innerhalb der Zellen genutzt.

Die beim CSGT2/S-Prozess hinzu gekommene zweite Polysiliziumlagen wird nur innerhalb der Standardzellen verwendet (grün). Sie ermöglichte die höhere Integrationsdichte und erklärt die deutlich unterschiedliche Architektur im Vergleich zum U1500. Die Rahmenfarbe der Pfeile zeigt auf oder unter welcher Lage sich die jeweilige Lage an dieser Stelle befindet. Die optische Erscheinung ändert sich dabei oft.

Die untere Polysiliziumlage (rosa) ist etwas feiner strukturiert als die Obere. Sie stellt auch die Gateelektroden dar. Die untere Polysiliziumlage realisiert außerdem die Kontakte zum Verdrahtungsbereich. Die Strukturen der Polysiliziumlagen sind durch die Metalllage hindurch einigermaßen gut zu erkennen. Wenn sich aber die Kanten der beiden Polysiliziumlagen unterhalb der Metalllage kreuzen, ist es oftmals schwierig die Leitungsführung zu identifizieren.

Unter allen Strukturen befinden sich die aktiven Bereiche (weiß). Die zugehörigen Kanten sind deutlich zu erkennen. An diesen Stellen wurden Fenster in das dicke Siliziumoxid geätzt, das ansonsten den ganzen Wafer überzieht. Nur in diesen Fenstern bilden sich Transistoren aus, wenn man einen Streifen des unteren Polysiliziums darauf aufbringt.

Der aktive Bereich und die drei Verdrahtungslagen können nicht beliebig miteinander verbunden werden. Eindeutig zu erkennen sind die Kontakte zwischen der zweiten Polysiliziumlage und dem aktiven Bereich (rot) und zwischen der ersten und der zweiten Polysiliziumlage (orange). Die Metalllage kann offensichtlich nur die zweite Polysiliziumlage kontaktieren (gelb). Will man mit der Metalllage die erste Polysiliziumlage oder den aktiven Bereich kontaktieren, so muss dies über die zweite Polysiliziumlage erfolgen. Dadurch ergeben sich teilweise Kontakte, die übereinander liegen und Bereiche, die komplizierter erscheinen als sie auf den ersten Blick sein müssten.

Die aktiven Bereiche sind immer mindestens zweigeteilt. In den oberen Bereichen der Zellen (roter Rahmen) befinden sich nur p-Kanal MOSFETs. In den unteren Bereichen sind nur n-Kanal MOSFETs zu finden (blauer Rahmen). Die p-Kanal MOSFETs, die üblicherweise schlechtere Spezifikationen haben, wurden entsprechend größer ausgeführt. Die aktiven Bereiche sind an mehreren Stellen mit Vss (blaue Flächen) und Vdd (rote Flächen) verbunden. In dieser Zelle ist der Vss-Kontakt in der unteren linken Ecke etwas unübersichtlich. Das ergibt sich durch die erweiterte Nutzung der zweiten Polysiliziumlage. Der rechteckige Kontakt verbindet die Metalllage mit der zweiten Polysiliziumlage. Diese erstreckt sich dann nach rechts und oben und ist über zwei runde Kontakte mit zwei Flächen des aktiven Bereichs verbunden.

Im rechten Bild sind die Flächen der ersten Polysiliziumlage farbig markiert. Gemeinsame Potentiale tragen die gleiche Farbe. Wo das Polysilizium die aktiven Bereiche bedeckt, bildet sich ein Transistor aus. Die unterschiedlichen Kontaktmöglichkeiten an der oberen und unteren Kante der Standardzelle sind gut zu erkennen.

Die Verbindungen über die zweite Polysiliziumlage und die Metalllage sind gestrichelt markiert. Ungefähr in der Mitte der Zelle findet sich ein Bereich, in dem die Zuordnung der Konturen sehr schwierig ist ("?"). An solchen Stellen muss man mit dem Hintergrundwissen über vorhandenen Logikfunktionen arbeiten oder die Schaltung in Teilen aufzeichnen, um dann Rückschlüsse auf den Rest ziehen zu können.

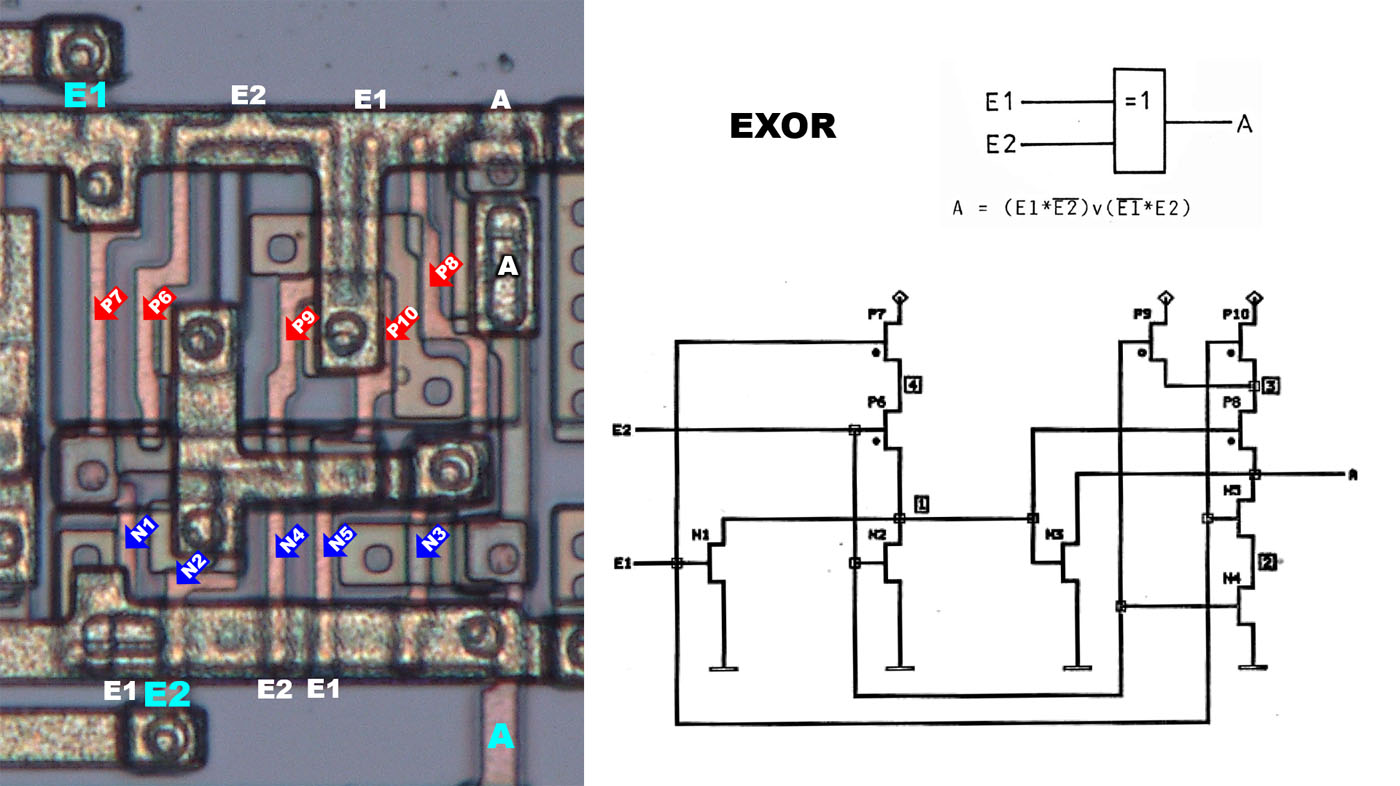

Mit dem Wissen über den Aufbau und die Funktionsweise der Strukturen kann man schließlich die Transistoren markieren. Die Rückerkennung der Schaltung ist einfacher als es auf den ersten Blick erscheint. Zum einen ist bekannt welche Logikgatter vorhanden sein müssen und zum anderen bestehen die Schaltungen meist nur aus relativ einfachen Parallel- und Serienschaltungen von Transistoren.

Hier handelt es sich hier um ein EXOR-Gatter, das fünf p-Kanal und fünf n-Kanal MOSFETs enthält. Der Schaltplan stammt aus dem Standardzellenkatalog des U1500. Für eine weitere Analyse der Schaltung ist eine ordentliche Dokumentation der Standardzellen und ihrer Kontakte extrem wichtig.

U1525FC007 Zentrum für Mikroelektronik Dresden Teil 2