Der LMC662 ist ein Zweifach-Operationsverstärker mit sehr respektablen Spezifikationen. Die hier vorliegende Variante LMC662AMJ ist für einen Temperaturbereich von -55°C bis +125°C freigegeben. Wie sich noch zeigen wird, basiert der LMC662 auf dem Vierfach-Operationsverstärker LMC660.

Der LMC662 kommt mit einer einfachen Versorgungsspannung zwischen 5V und 15V aus. Die Stromaufnahme beträgt weniger als 0,75mA. Der zulässige Eingangsspannungsbereich schließt das negative Versorgungspotential mit ein. Der Ausgang kann über den vollständigen Versorgungsspannungsbereich ausgesteuert werden. Abhängig vom Arbeitspunkt ermöglicht die Ausgangsstufe Ströme bis zu 40mA. Der LMC662 erreicht eine Slewrate von 1,1V/µs und eine Grenzfrequenz von 1,4MHz.

Der extrem niedrige Biasstrom von typischerweise 2fA wird durch eine CMOS-Eingangsstufe erreicht. Dennoch ist die Rauschspannung mit 22nV/√Hz sehr niedrig. Das Stromrauschen beträgt 0,2fA/√Hz. Die Offsetspannung liegt typischerweise bei 1mV mit einem Temperaturdrift von 1,3µV/°C.

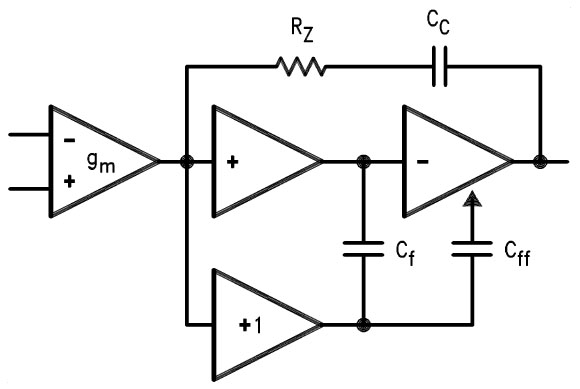

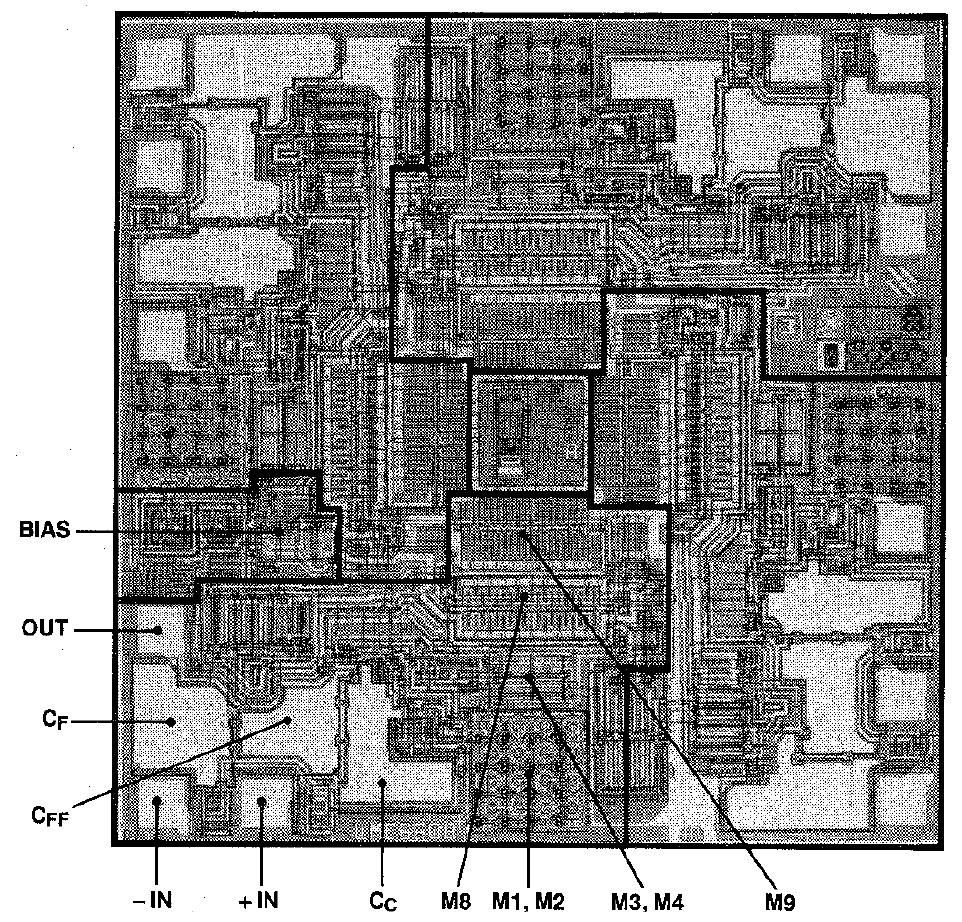

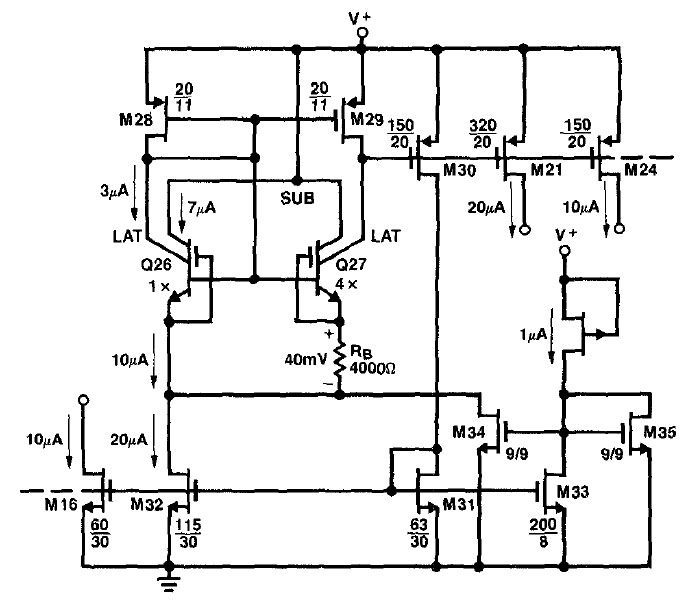

Im Datenblatt des LMC662 zeigt National Semiconductor den etwas ungewöhnlichen Aufbau des LMC662. Auf den Differenzverstärker am Eingang folgt eine Spannungsverstärkerstufe, die aus einem nicht invertierenden und einem invertierenden Verstärker besteht. Über dieser Spannungsverstärkerstufe befindet sich der Kompensationskondensator Cc. Ein Pufferverstärker bedient zwei Kapazitäten, die als Vorsteuerung in die Spannungsverstärkerstufe eingreifen. Einen klassischen, als Puffer aufgebauten Ausgangsverstärker besitzt der LMC662 nicht.

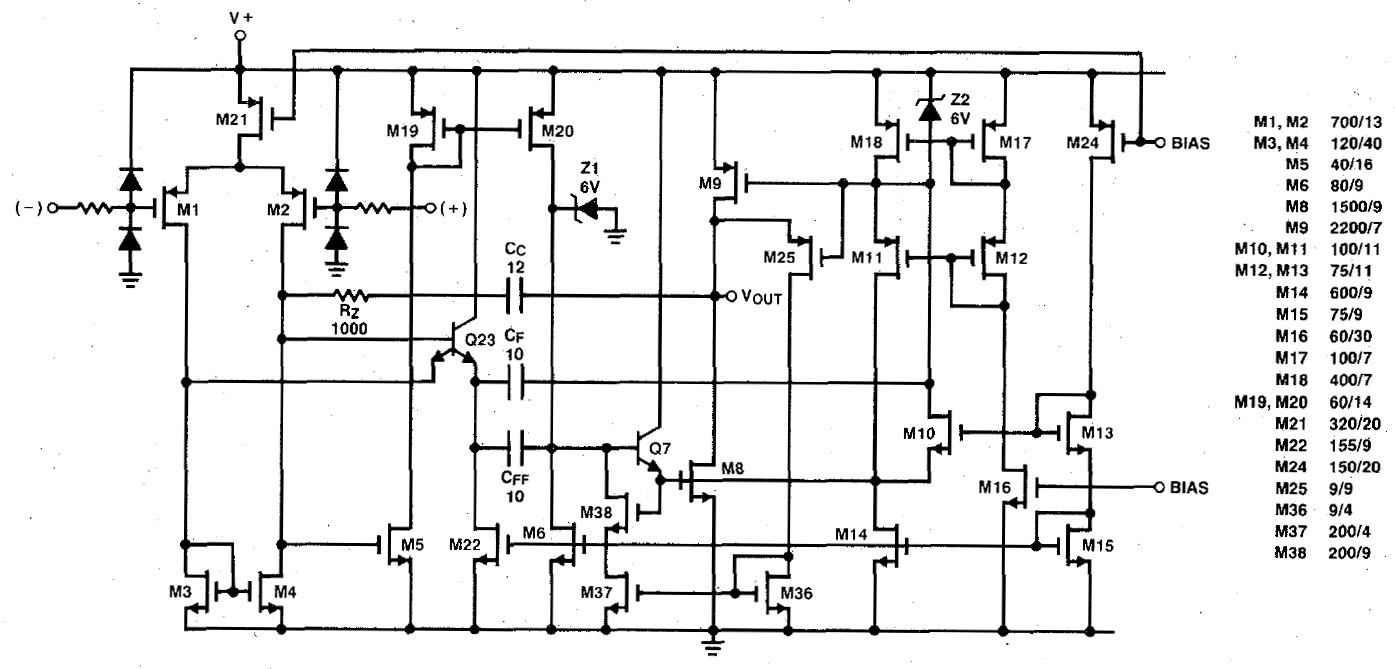

Dennis M. Monticelli beschreibt den LMC662 sehr ausführlich im IEEE-Artikel "A Quad CMOS Single-Supply Op Amp with Rail-to-Rail Output Swing". Dort ist die vollständige Schaltung inklusive der Auslegung der einzelnen Transistoren abgebildet.

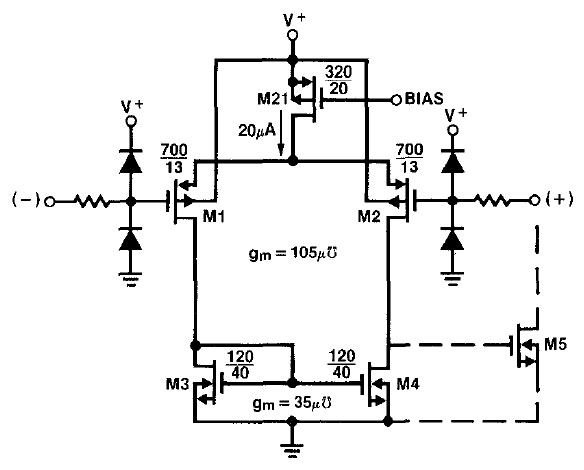

Der Differenzverstärker am Eingang ist klassisch mit einer Stromquelle und einem Stromspiegel aufgebaut. Das IEEE-Paper erklärt, dass als Eingangstransistoren p-Kanal MOSFETs ohne zusätzliche Dotierung zur Anpassung der Thresholdspannung eingesetzt wurden. Diese Art von MOSFETs würden am wenigsten rauschen.

Der LMC662 besitzt keine Möglichkeit die Offsetspannung abzugleichen. Trotzdem sind die Werte für Offsetspannung und Drift verhältnismäßig gut.

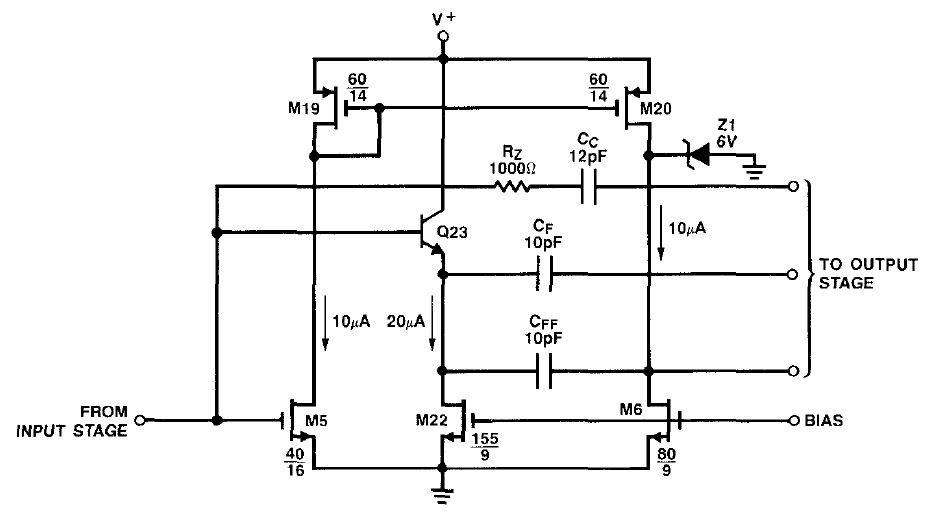

Die Transistoren M5, M19, M20 und M6 verstärken das Ausgangssignal des Differenzverstärkers und treiben damit die Ausgangsstufe. Das IEEE-Paper gibt einen Verstärkungsfaktor von 40dB an. Z1 begrenzt die Spannung und damit den Strom am Ausgang des LMC662.

Q23 und M22 stellen die Verstärkerstufe dar, die die Kondensatoren der Vorsteuerung treibt. Cff ist mit dem Ausgang der hier zusehenden Verstärkerstufe verbunden. Cf führt zur Ausgangsstufe.

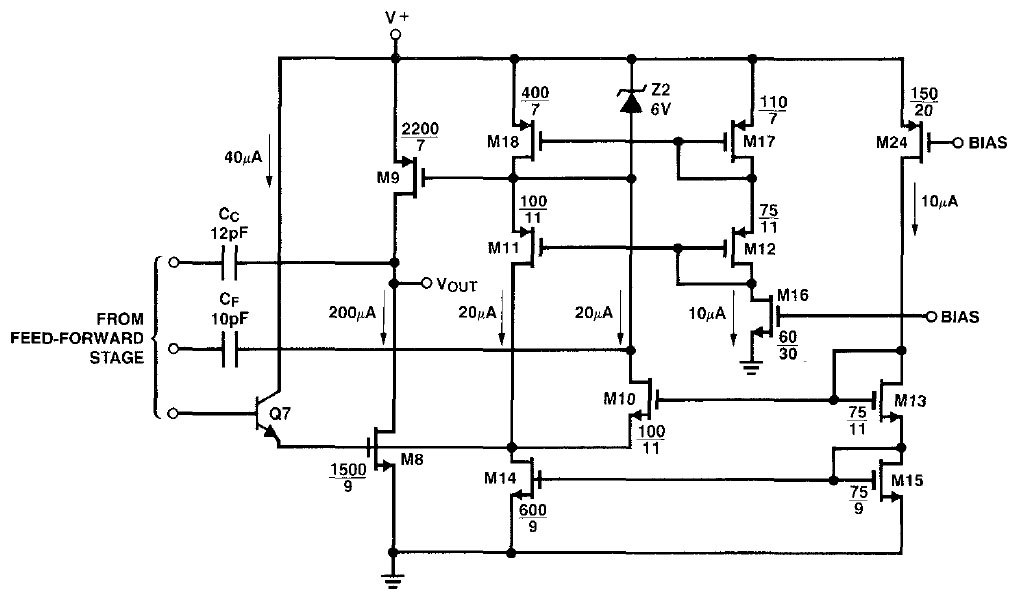

Der Transistor Q7 stellt den Treiber für die Push/Pull-Ausgangsstufe M8/M9 dar. Die relativ komplexe Verschaltung der Arbeitspunkteinstellung sorgt laut IEEE-Paper dafür, dass der Ruhestrom der Endstufe nicht von der Versorgungsspannung und Prozessvariationen abhängig ist.

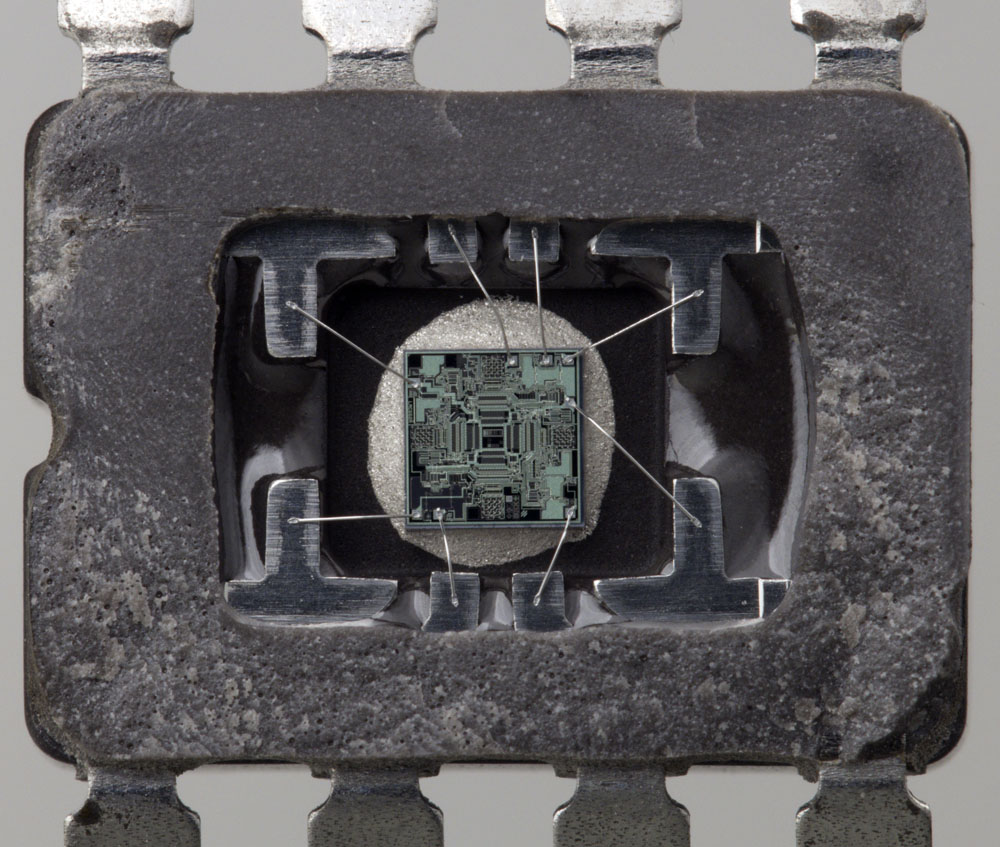

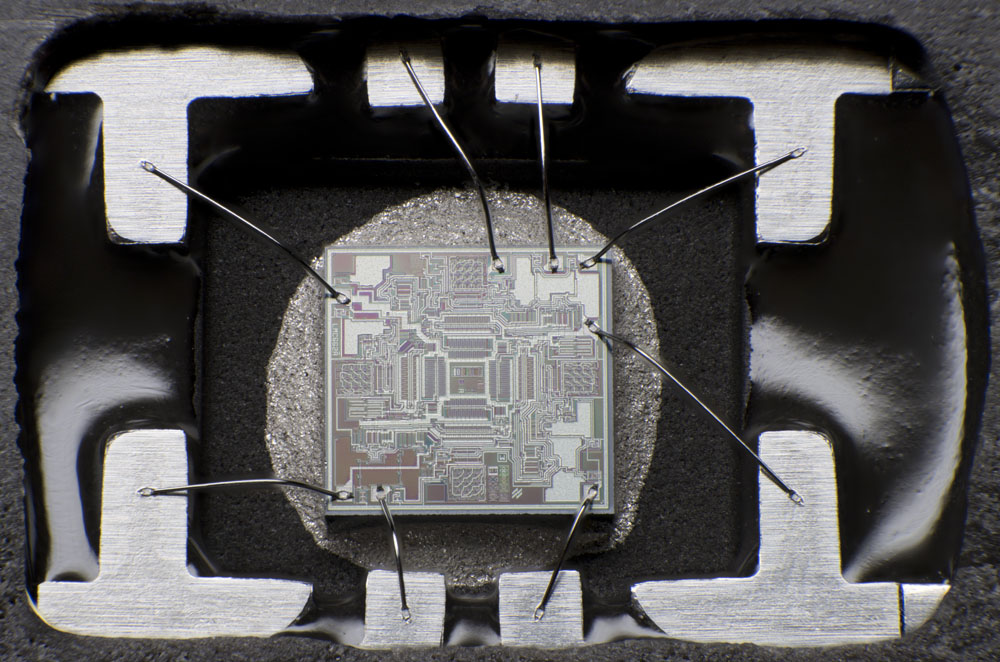

Die Variante LMC662AMJ, die für den maximalen Temperaturbereich spezifiziert ist, befindet sich in einem Keramikgehäuse.

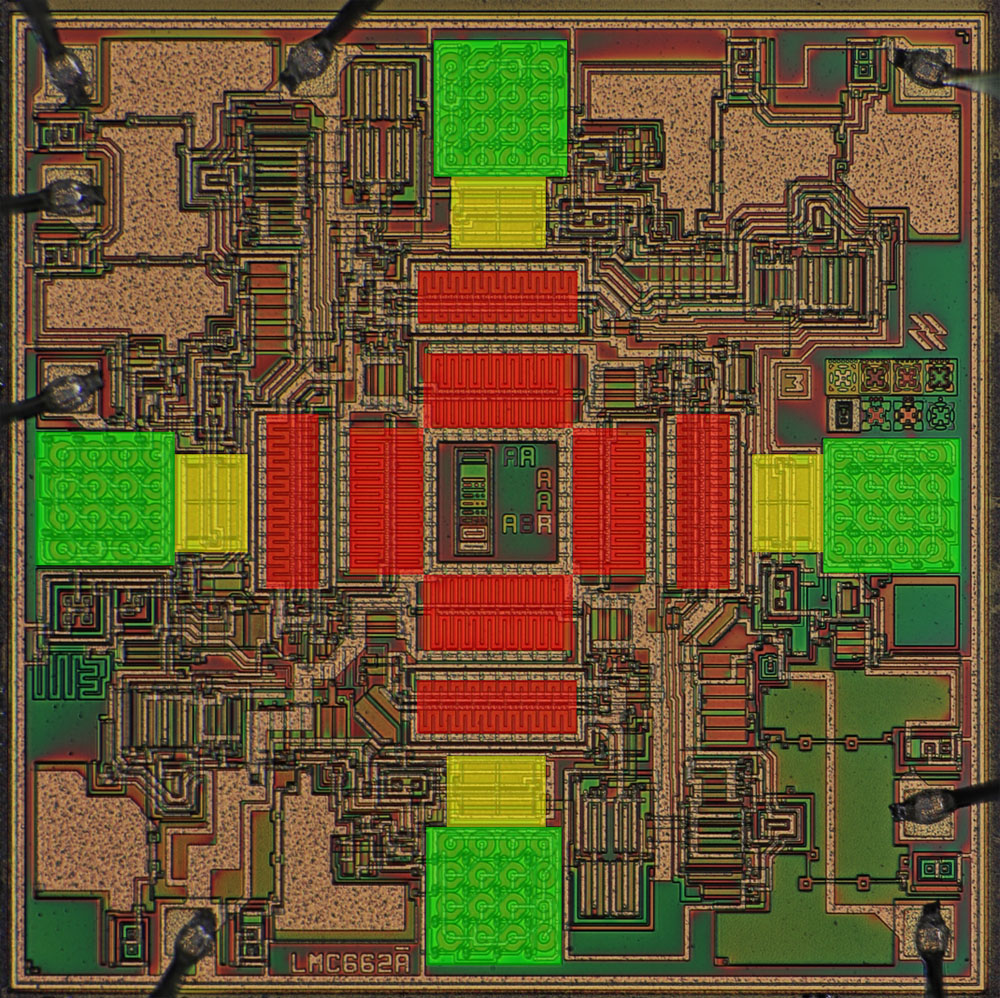

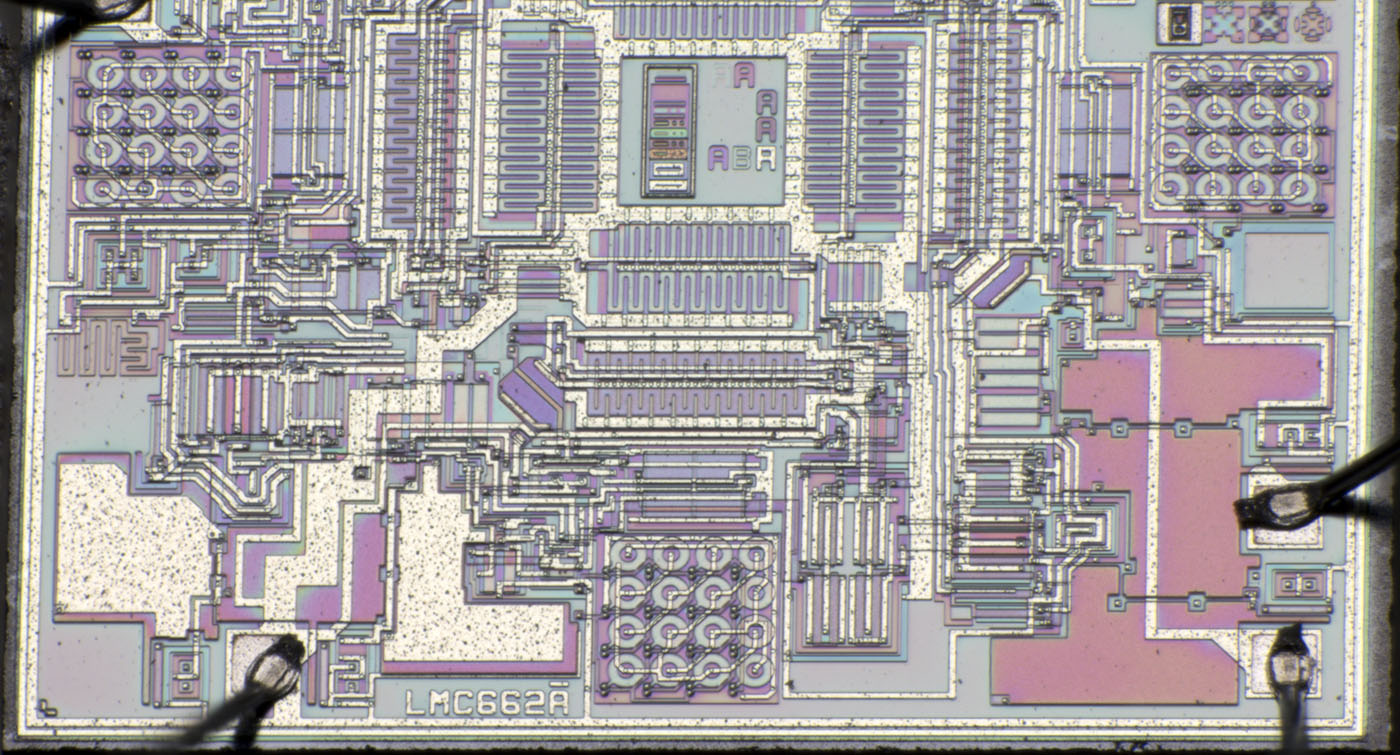

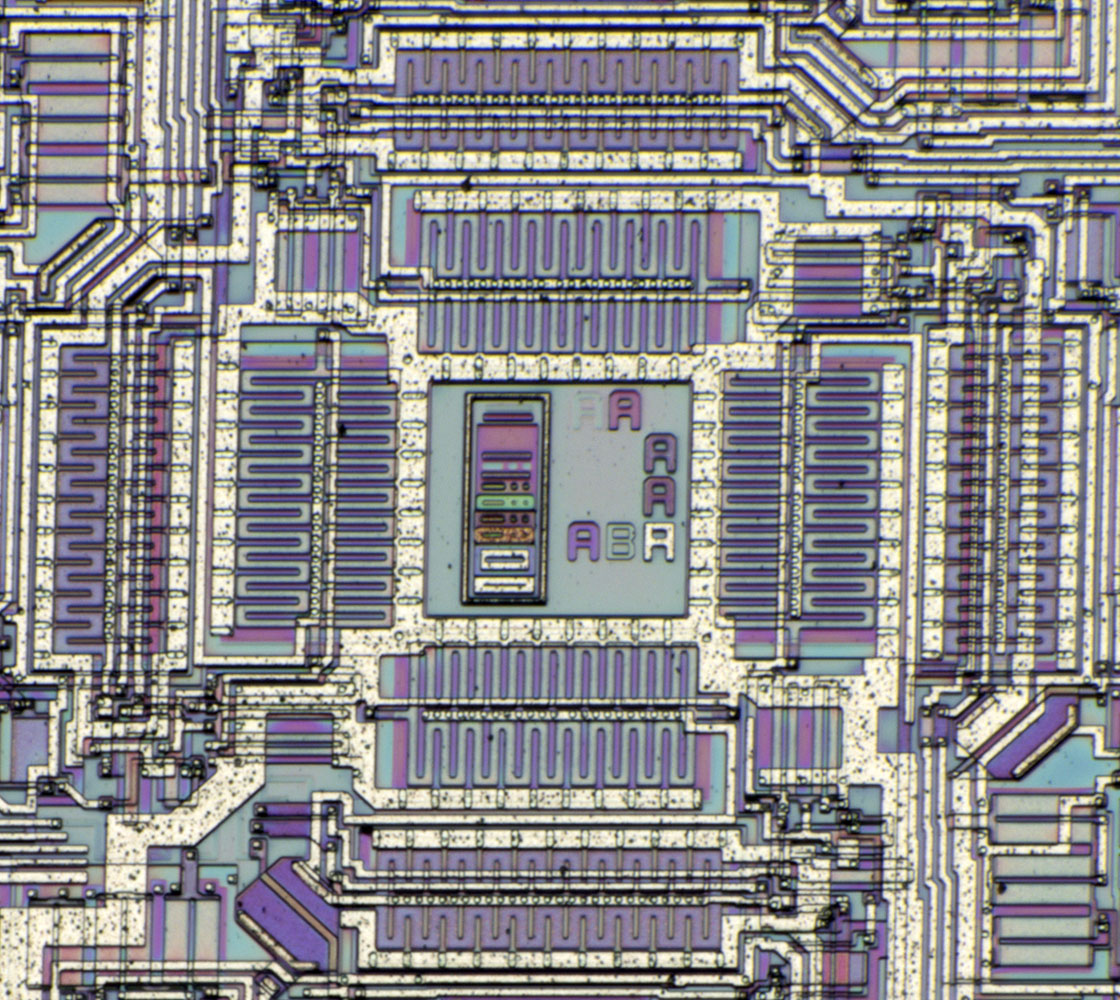

Die Kantenlänge des Dies beträgt 1,9mm. Das IEEE-Paper gibt an, dass bei der Herstellung ein 4µm Prozess mit zwei Lagen Poliysilizium zum Einsatz kommt, der eigentlich für digitale CMOS-Schaltungen optimiert wurde. Das kann sehr nützlich sein, wenn man diesen Operationsverstärker mit digitalen Schaltungsteilen kombinieren will.

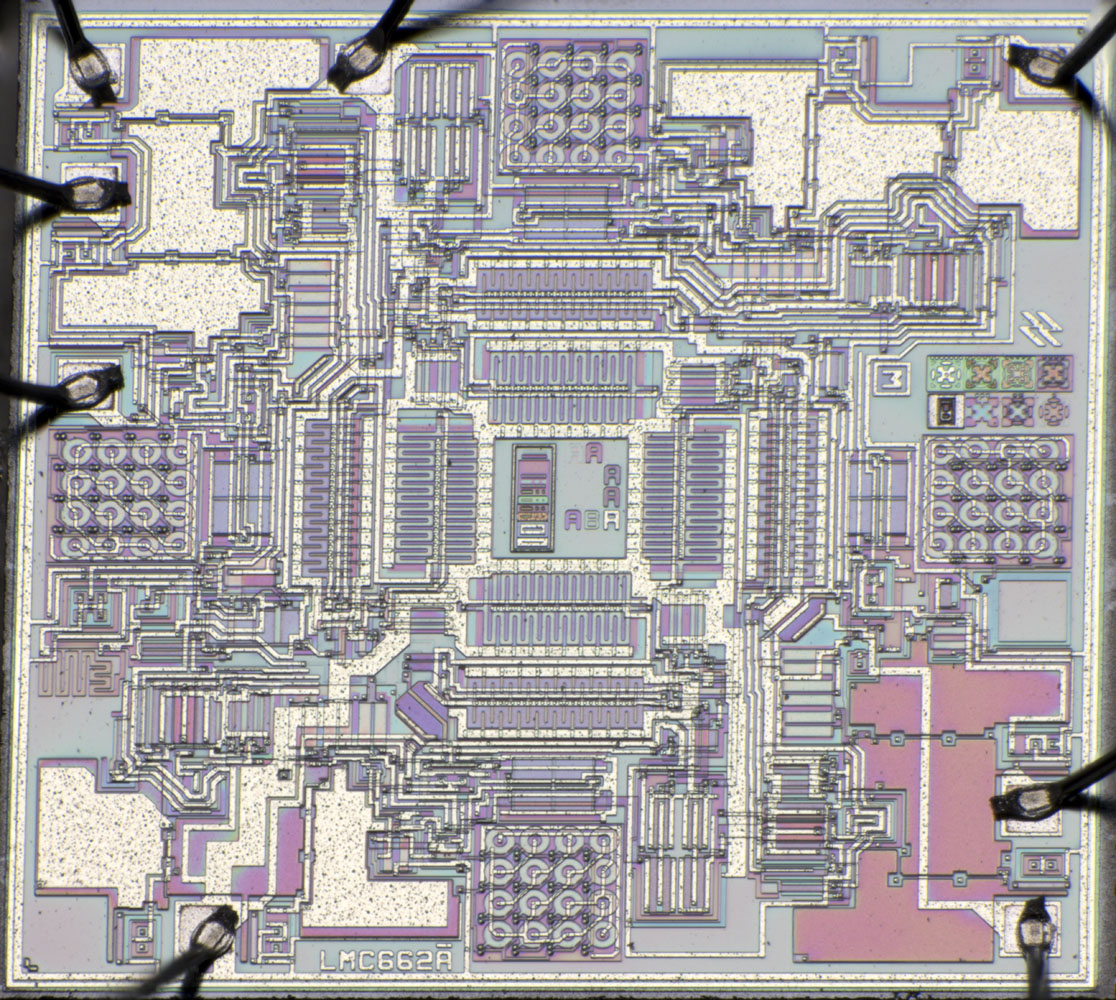

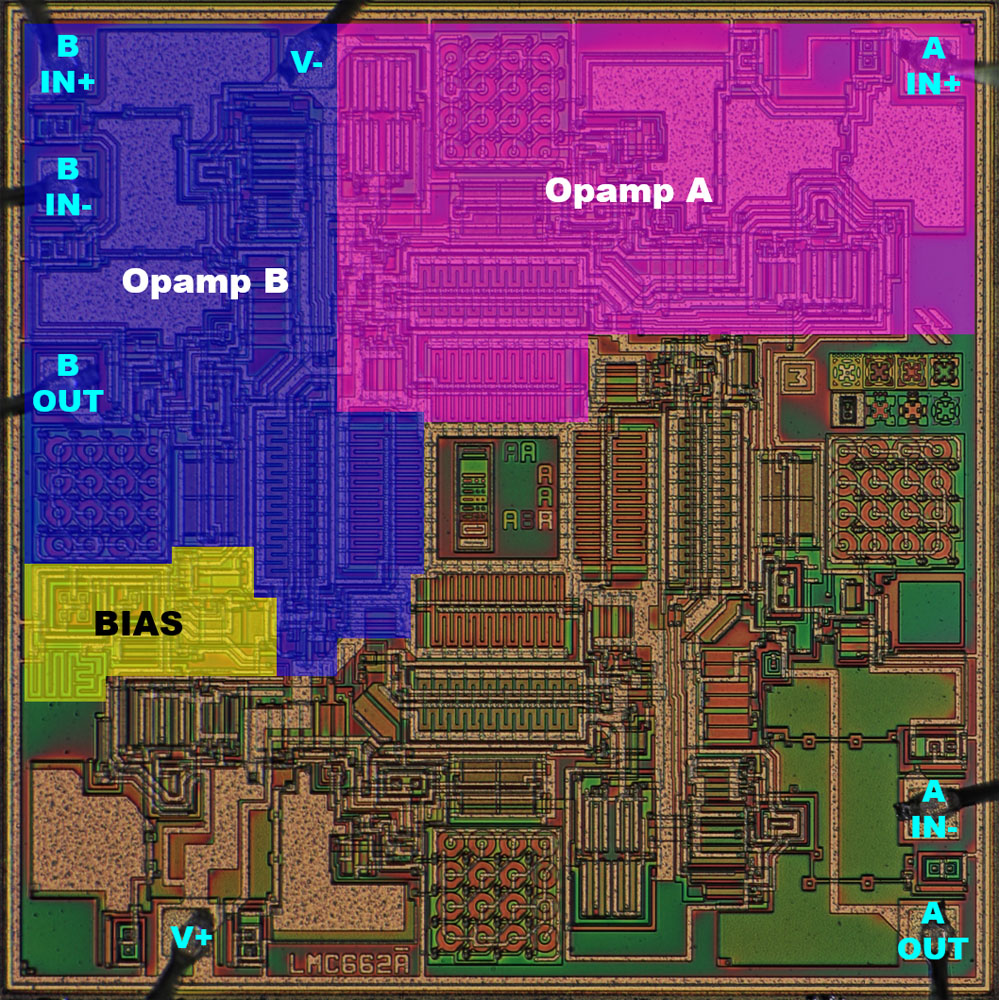

Wie sich noch zeigen wird, teilen sich der Vierfach-Operationsverstärker LMC660 und der Zweifach-Operationsverstärker LMC662 im Grunde das gleiche Die. Sie unterscheiden sich lediglich durch die Metalllage. In der Metalllage ist die Bezeichnung LMC662 abgebildet. Der Buchstabe A könnte für eine erste Revision stehen.

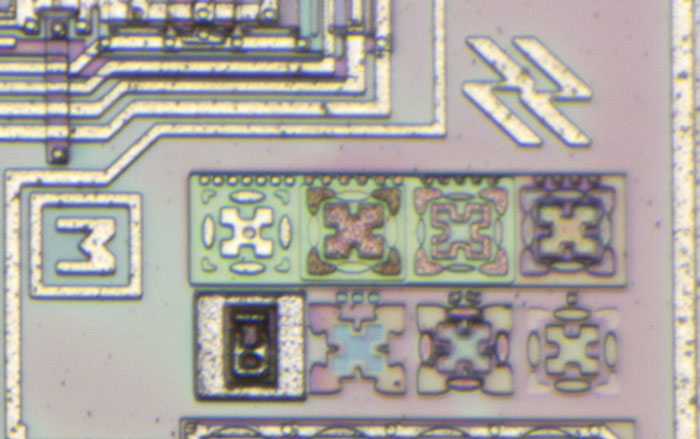

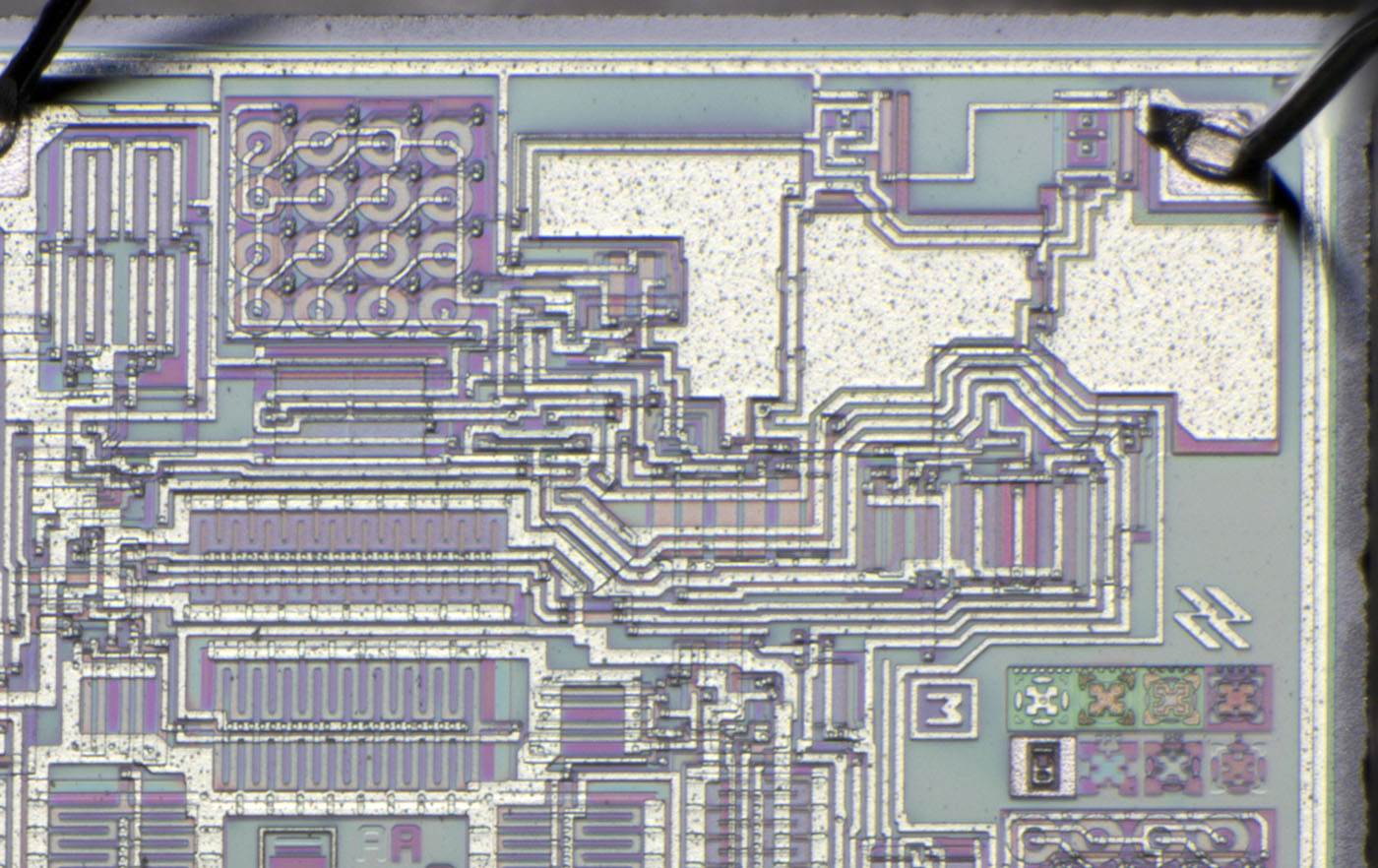

In der Mitte des Dies sind sieben Maskenrevisionen abgebildet. Demnach wurde eine Maske einmal überarbeitet. Die Strukturen neben den Maskenrevisionen ermöglichen eine Bewertung der Abbildungsqualität.

An der rechten Kante sind unter dem National Semiconductor Logo sieben komplexe Strukturen abgebildet. Punkte oberhalb der Strukturen nummerieren die Strukturen. Hier kann neben der Abbildungsleistung die Ausrichtung der Masken gegeneinander geprüft werden.

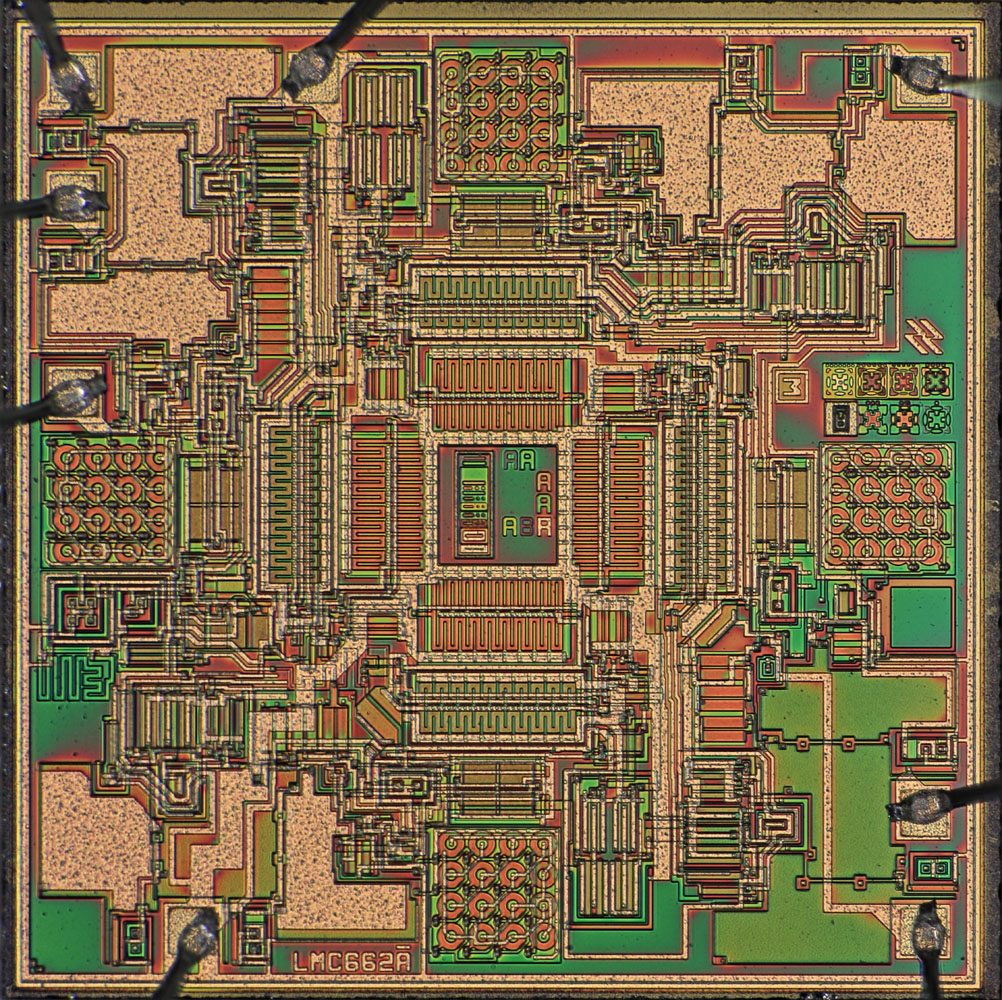

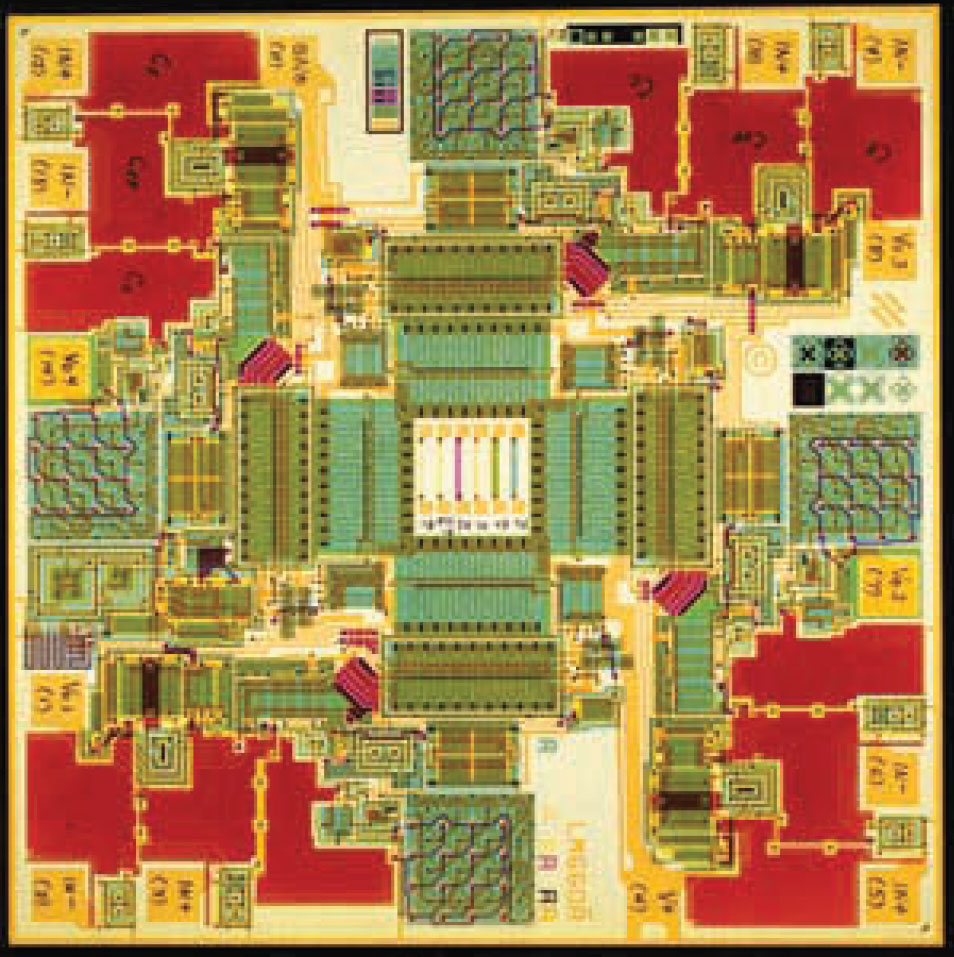

Die Zeitschrift "Electronics Design Network" (11/2012) enthält ein Bild des Vierfach-Operationsverstärkers LMC660. Es handelt sich demnach um eine Darstellung, die der Fehlersuche diente. Die verschiedenen Masken wurden mit verschiedenen Farben auf mehrere Folien gedruckt. Legt man die Folien übereinander, so erzeugen sich überlappende Schichten Mischfarben und man kann die Strukturen effizient überprüfen.

Die bereits referenzierte IEEE-Veröffentlichung enthält ebenfalls ein Bild der Strukturen des LMC660. Dicke schwarze Striche arbeiten die Flächen der vier Operationsverstärker heraus. Im linken Bereich ist zusätzlich die Arbeitspunkteinstellung markiert.

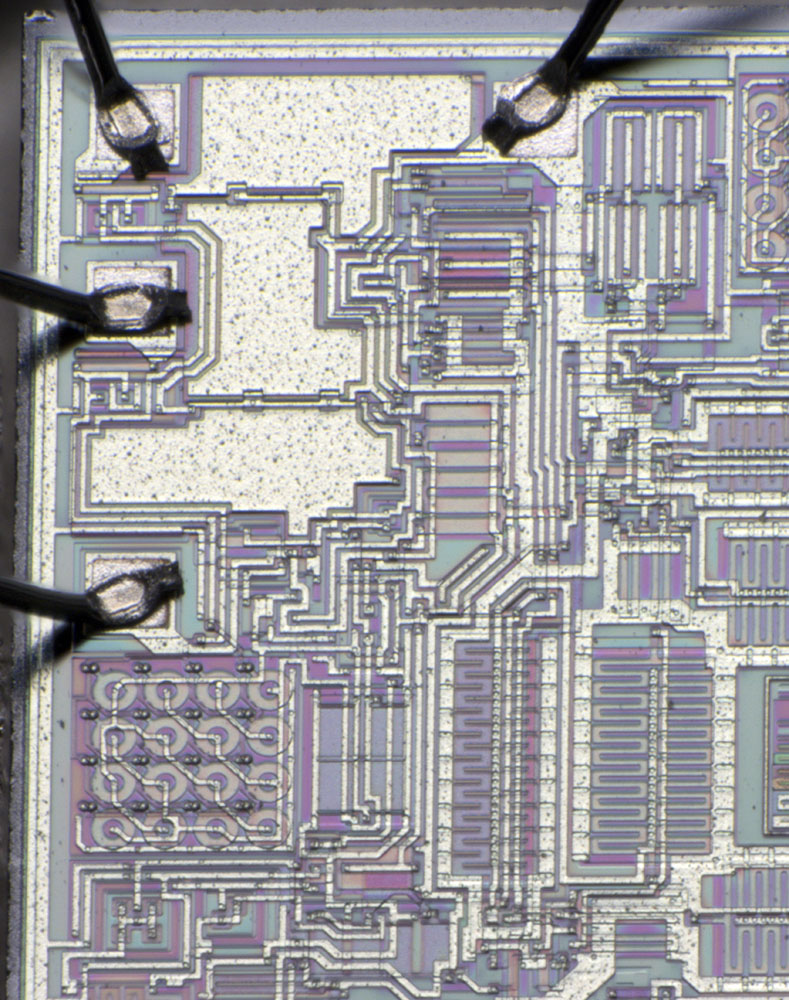

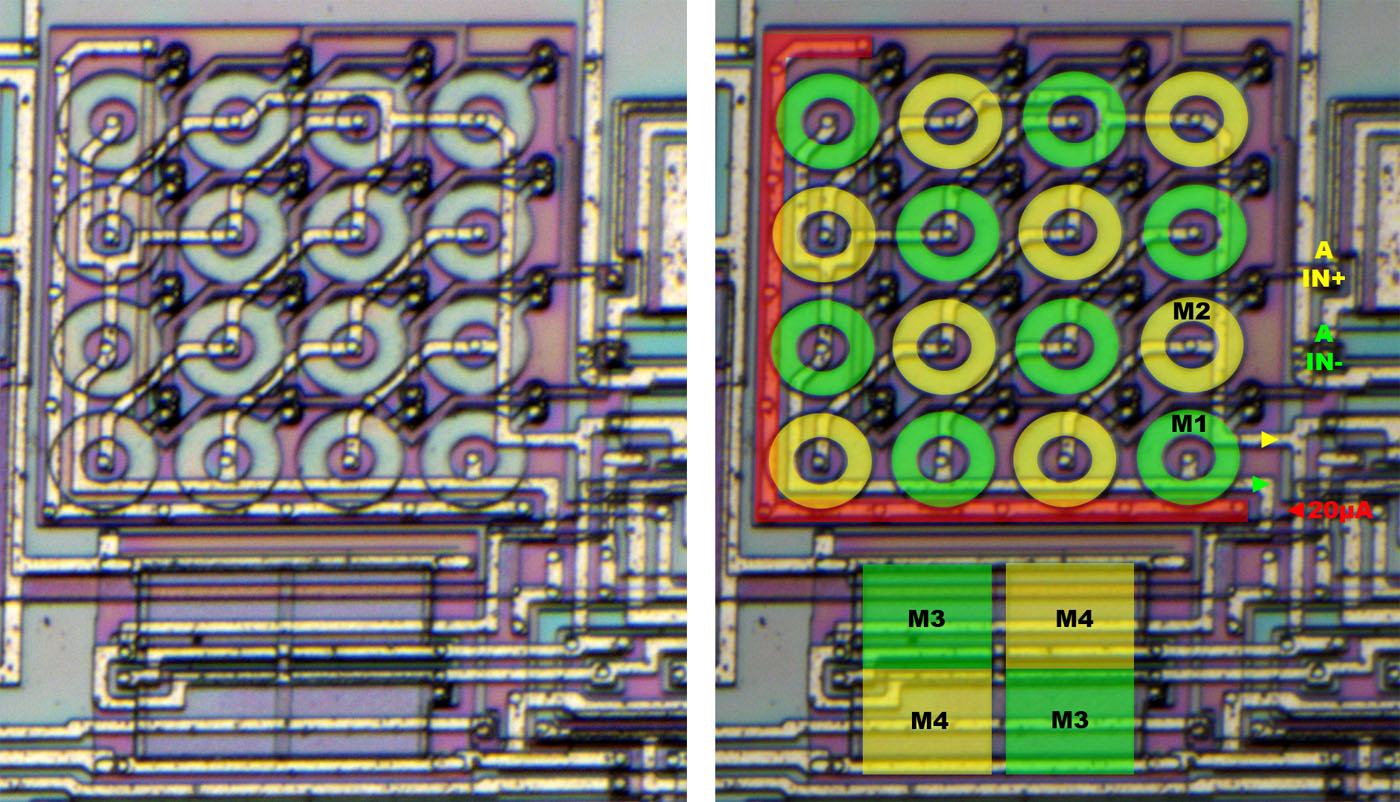

Die Eingangstransistoren M1/M2 (grün) und die Transistoren des zugehörigen Stromspiegels M3/M4 (gelb) befinden sich jeweils an Stellen, wo sie möglichst wenig negativ beeinflusst werden. Problematisch sind zum einen thermische Gradienten, die sich vor allem durch die Verlustleistung der Endstufentransistoren (rot) ergeben. Die Ausrichtung von Endstufen und Eingangstransistoren auf den Symmetrieachsen sorgt dafür, dass sich die thermischen Gradienten auf beide Pfade des Differenzverstärkers sehr ähnlich auswirken und so kompensieren. Ein weiterer Punkt sind mechanische Belastungen, die sich bei der Integration in das Gehäuse ergeben. Auch diese Belastungen sind auf den Symmetrieachsen am geringsten.

Der Zweifach-Operationsverstärker LMC662 nutzt abgesehen von der Metalllage das gleiche Design wie der Vierfach-Operationsverstärker LM660. Ungenutzt bleiben hier die zwei Operationsverstärker an der rechten und der unteren Kante.

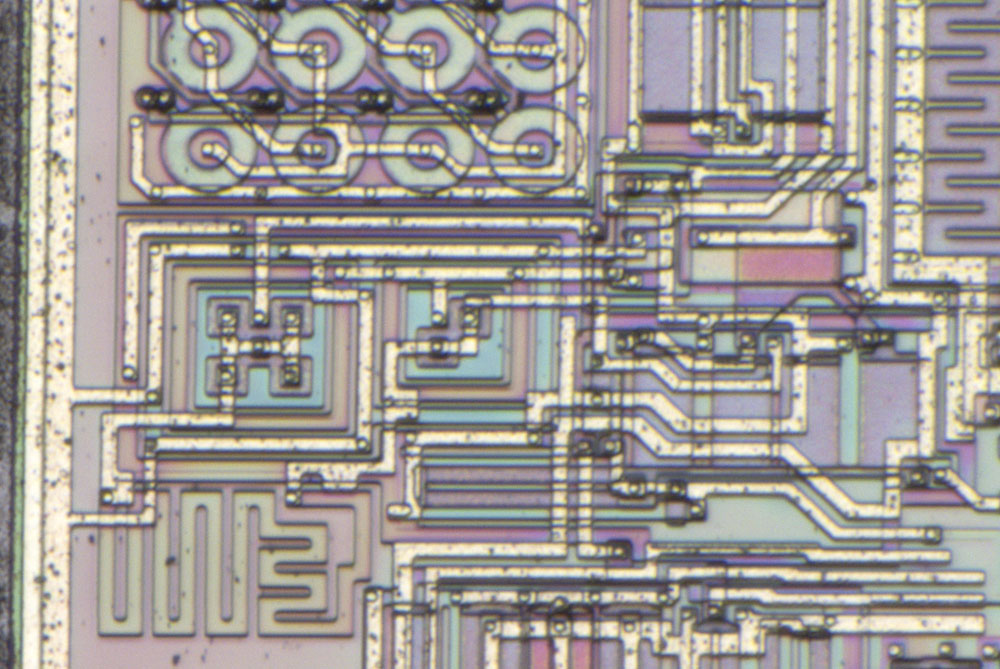

Die einzelnen Komponenten der Operationsverstärker sind trotz der zwei Polysiliziumlagen noch recht gut zu erkennen. Besonders auffällig sind neben den Eingangs- und den Endstufentransistoren die drei großen Kondensatoren.

Die Eingänge der Operationsverstärker sind mit einer Schutzschaltung ausgestattet. Laut dem IEEE-Artikel befindet sich dort ein 20Ω-Strombegrenzungs-Widerstand, gefolgt von Schutzdioden zu den Versorgungspotentialen. Das Vorhandensein dieser Dioden ist bemerkenswert, da deren Leckstrom so niedrig sein muss, dass sie den sehr kleinen Eingangsstrom des Operationsverstärkers nicht zu sehr anheben. In diesem Zusammenhang ist es verwunderlich, dass das IEEE-Paper einen summierten Leckstrom von 50fA angibt, während der Biasstrom typischerweise nur 2fA betragen soll. Es zeigt sich, dass frühe Datenblätter einen Biasstrom von 40fA spezifizieren. Entweder wurde der Prozess verbessert oder man konnte anfänglich schlicht keine geringeren Ströme messtechnisch bestimmen.

Unter der Metalllage befinden sich vier vollständige Operationsverstärker. Die Metalllage oberhalb der ungenutzten Operationsverstärker hat man stark modifiziert. Der Hauptgrund scheint das andere Pinning im kleineren Package zu sein. Um die Pins sinnvoll mit der Schaltung verbinden zu können, musste man die Bondpads versetzen.

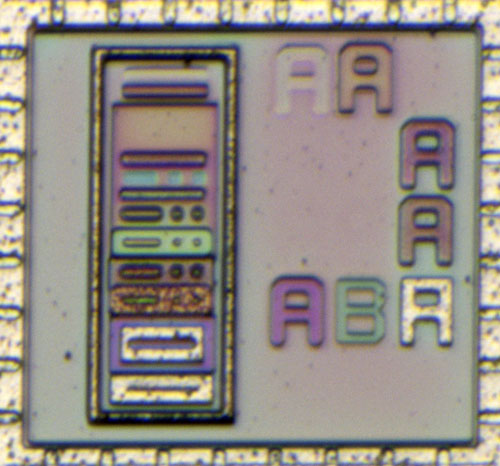

Die Eingangstransistoren M1/M2 bestehen aus jeweils acht kreisförmigen Elementen, die so ineinander verschachtelt sind, dass sich thermische Gradienten auf beide Pfade des Differenzverstärkers möglichst gleich auswirken. Eine ähnlich starke Verflechtung ist im OPA627 umgesetzt. Die Transistoren M3/M4, die den Stromspiegel des Differenzverstärkers darstellen, sind zumindest jeweils auf zwei Transistoren aufgeteilt und über Kreuz verschaltet.

Die Source-Kontaktierung (rot) ist unscheinbar. Das IEEE-Paper beschreibt allerdings, dass die unterschiedlichen Strecken zu den einzelnen Transistoren durchaus kritisch sind und zu einem unsymmetrischen Verhalten des Differenzverstärkers führen können. Demnach wurden 50 verschiedene Konfigurationen simuliert, bis die hier zu sehende Struktur als optimal erachtet wurde.

Die Highside- und die Lowside-Transistoren sind verhältnismäßig groß ausgeführt, damit sie die hohen Ausgangsströme tragen können.

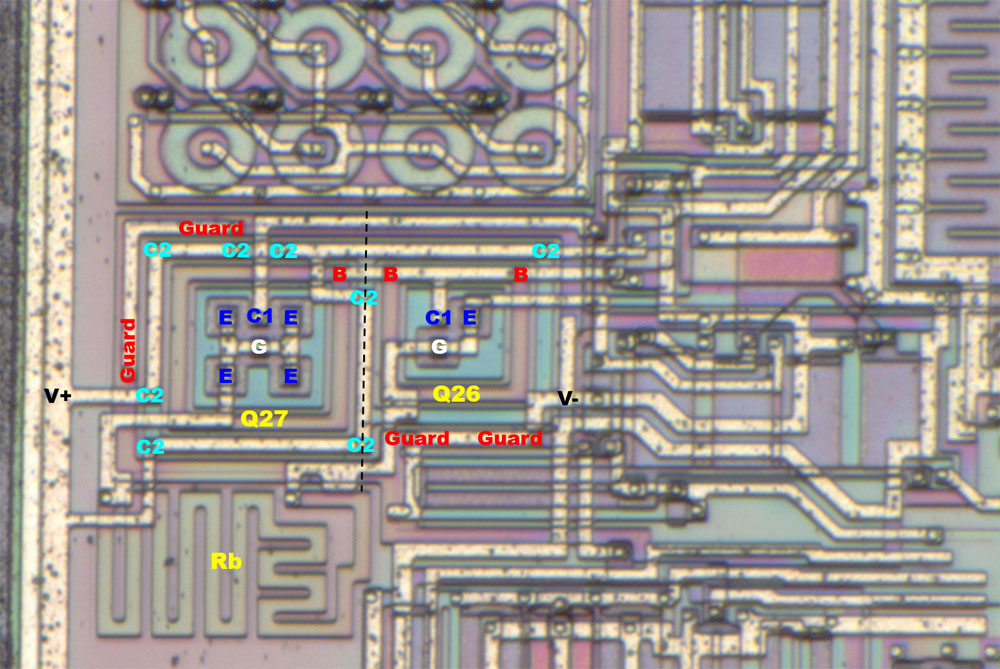

Auch in einem CMOS-Schaltkreis kann man eine Bandgap-Referenzspannungsquelle aufbauen. Sie basiert hier auf den zwei speziellen NPN-Transistoren Q26/Q27. Es handelt sich um teilweise laterale Bipolartransistoren, die sich innerhalb eines normalen CMOS-Prozesses darstellen lassen.

Den Aufbau eines solchen lateralen Bipolartransistors kann man der IEEE-Veröffentlichung "Photodetection With Gate-Controlled Lateral BJTs From Standard CMOS Technology" entnehmen. Der einzige Unterschied zum LMC662 ist, dass hier ein 3-Well-CMOS-Prozess zum Einsatz kommt, in dem ein zusätzlicher Nwell verfügbar ist. Im LMC662 stellt das Substrat die Schicht Nwell dar und die unterste Schicht Psub ist nicht vorhanden.

Ein n-Kanal MOSFET enthält von sich aus einen parasitären NPN-Transistor, der hier nachträglich rot eingefärbt wurde. Um diesen nutzen zu können, muss das Gate des MOSFETs so verschaltet werden, dass dieser Bereich immer sperrt. Die Konstruktion enthält einen zweiten, parasitären Kollektor. Dieser ist über das Substrat an das positive Versorgungspotential angebunden. Das bedeutet allerdings gleichzeitig, dass über diesen Kollektor ein Strom fließt, der proportional zum Strom durch den lateralen Kollektor ist. Damit der laterale Kollektor einen relevanten Anteil des Stroms übernimmt, muss dieser möglichst nah am Emitter platziert werden. Die Stromaufteilung wird durch Produktionsschwankungen stark beeinflusst und lässt sich nicht übermäßig gut kontrollieren. Die Verschaltung innerhalb der Bandgap-Referenz sorgt dafür, dass diese Toleranz keinen übermäßig großen Einfluss auf die Referenzspannung hat.

Von oben betrachtet sind derartige CMOS-NPN-Transistoren konzentrisch aufgebaut. Wie üblich für eine Bandgap-Referenz, besitzen die zwei Transistoren Q27/Q26 unterschiedlich große Emitterflächen. Im LMC662 beträgt das Verhältnis der Flächen 4:1.

Emitter und Gate sind miteinander verbunden. Hier im Bild ist der Unterschied auf Grund der kleinen Strukturen kaum zu erkennen. Die lila erscheinende Fläche ist die Gate-Elektrode, innerhalb derer sich die einzelnen Emitter befinden. Direkt um die Gate-Elektrode wird der laterale Kollektor C1 abgegriffen. Der Rahmen um dieses Konstrukt ist der Basisbereich, den wiederum der Kollektor C2 umgibt. Die C2-Kontakte führen zum Substrat und binden es lokal an das positive Versorgungspotential an. Der äußerste Rahmen muss eine hohe p-Dotierung enthalten. Er sieht genauso aus wie das Material des Widerstands Rb, der laut IEEE-Paper eine hohe p-Dotierung enthält. Der Rahmen ist mit dem negativen Versorgungspotential verbunden. Vermutlich handelt es sich um eine Schutzstruktur, die verhindern soll, dass freie Ladungsträger in benachbarte Schaltungsteile abfließen.